## 3GPP TSG RAN WG1 Busan, Korea, May21-25, 2001

Agenda Item: AH24 (HSDPA)

Source: Mitsubishi Electric

Title: DTX Proposal for multi-level modulation in HSDPA

Document for: Discussion

#### 1 Introduction

In this document, new discontinuous transmission (DTX) method for higher order modulations used in HSDPA is proposed.

DTX has been proposed for QPSK modulation in 3GPP release 99 but DTX for higher order modulations such as 16QAM and 64 QAM used in HSDPA has not been studied up to now. Generally in conventional DTX method used for QPSK, DTX bits can happen either in two bits as one QPSK symbol or in one bit as in-phase or quadrature part of QPSK symbol. And then in-phase or quadrature DTX bit is in transmission off in case of one DTX bit and the whole QPSK symbol is in transmission off in case of two consequent DTX bits. However the conventional DTX method can not be applied to higher order modulations (more than 4) directly because that the number of possible DTX combination is too large and also the number of signals in constellation is too large.

To use DTX in HSDPA is effective, because it can easily increase the system capacity by reducing average transmission power.

In HSDPA, enhanced version of HS-DSCH channel coding is needed in order to use higher modulation, shorter frame size, etc. Channel coding scheme can be classified to 4 types, in order to reduce complexity, while 7 MCS levels are defined in current 3G TR25.848. 4 types consist of QPSK (MCS=1,2,3), 8PSK(MCS=4), 16QAM(MCS=5,6), 64QAM(MCS=7), and the number of bits of physical channel mapping is different among these modulations.

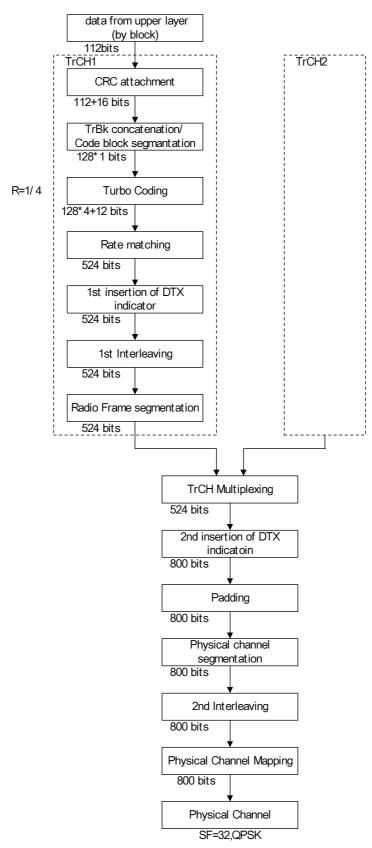

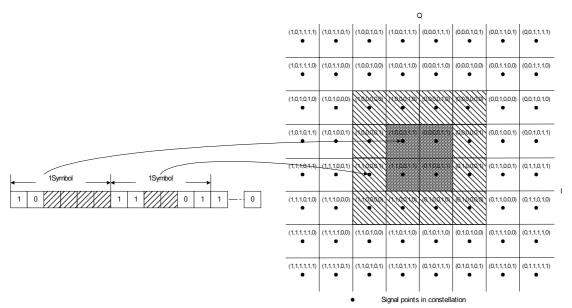

Figure 1 shows the channel coding scheme of the conventional QPSK (MCS=1) case. It is assumed that HSDPA TTI=3.33ms, TrBk size=112bits/3.33ms, CRC=16bits, and CRC is attached in every HSDPA TTI. As shown in Figure 1, 276 bits DTX is needed. Because many MCS levels are used, it is preferable to apply the same DTX insertion methods to several MCS level cases in order to make implementation easy.

In HSDPA, MCS level, number of codes, etc., are informed to UE by associated DPCH signaling, so DTX bits may be changed at any constellation positions.

So, the point is, how to transfer the DTX bits and map DTX inserted symbols to the signal constellation.

How to group DTX bits, insert DTX bits into symbols and then map DTX bits inserted symbols to the signal constellation with the minimal average transmission power is the key issue we want to solve in this document. We propose two DTX grouping and mapping methods, which have good power reduction effect in next section.

Figure 1 HS-DSCH Channel Coding Flow (conventional)

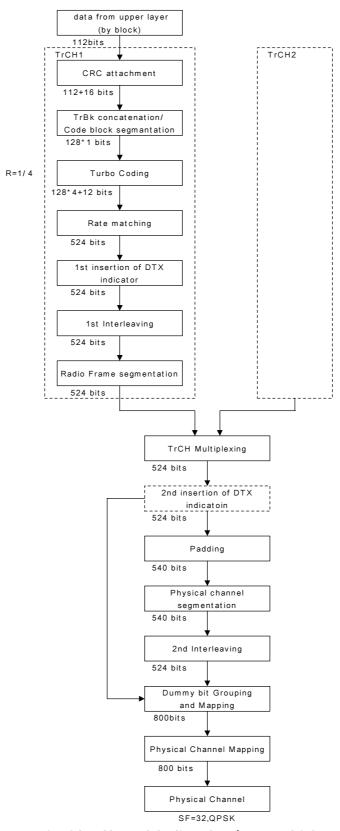

Figure 2 HS-DSCH Channel Coding Flow (Proposed Scheme)

## 2 Proposal of DTX method

As shown in Figure 1, in conventional channel coding, 2<sup>nd</sup> insertion of DTX indication is done before 2<sup>nd</sup> interleaving so the size of consequent DTX bits may change and has no regulation. And when insert DTX bits into symbols, the DTX bit location inside symbols also changes randomly. In order to reduce the average transmission power, it is necessary to group DTX bits, insert DTX bits into symbols with some regulations and map the DTX inserted symbols to signal constellation also with some regulations which results in DTX inserted symbols correspond to most inner points of signal constellation. And the DTX grouping and mapping criterion is to reduce average transmission power to the minimal value.

Our proposal can be used in ordinary higher order modulation receiver regardless if DTX is used or not.

Proposed scheme of channel coding for HSDPA is shown in Figure 2, in which the conventional channel coding procedure remained unchanged while dummy bit insertion and mapping process is added. And it is proposed that 2<sup>nd</sup> insertion of DTX indication block (plotted in dashed block) is skipped, while the DTX insertion function is done by dummy bit insertion and mapping block instead. Note that dummy bit grouping and mapping process is different from the conventional DTX indication. Because it has two new steps, one is group the DTX bits into desirable blocks with desirable size, another is to insert DTX bits into proper bit location of symbol and exchange them to the proper dummy bits "0" or "1" which results in the dummy bits inserted symbols corresponds to the most inner points of signal constellation.

There are 2 proposals of dummy bit insertion and mapping method, one is 1 symbol grouping method, and another is 1/2 symbol grouping method.

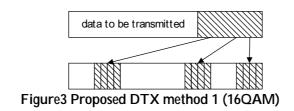

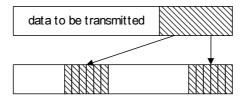

- Method1 (1 symbol size DTX grouping method) Method1 is demonstrated in Figures 3-6.

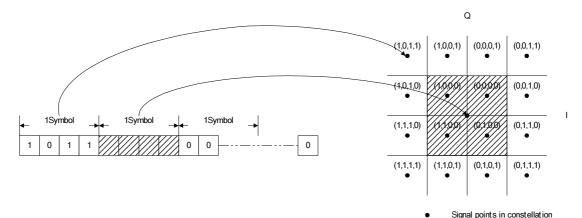

- (1) As shown in Figure 3 and Figure 5, necessary DTX bits are grouped regularly into DTX symbols with length of one symbol size (4 bits in case of 16QAM, 6bits in case of 64QAM). And the DTX items are dispersed to the whole frame in order to average transmission power.

- (2) The DTX symbols are mapped to the origin point, which means DTX symbols are not transmitted as demonstrated in Figures 5-6.

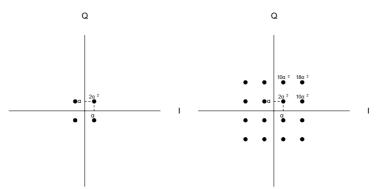

Figure 4 Bit sequence and the constellation (16QAM)

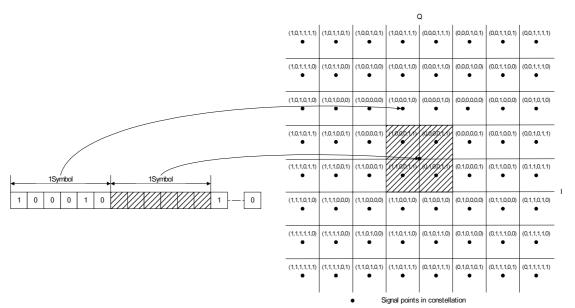

Figure 5 Proposed DTX method 1 (64QAM)

Figure Bit sequence and the constellation (64QAM)

Signal points in constellation

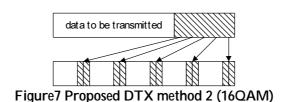

- Method2 (1/2 symbol size DTX grouping method) Method2 is demonstrated in Figures 7-10.

- In case of 16QAM, the DTX grouping and mapping regulation is as follows:

- (1) As shown in Figure 3 and Figure 5, necessary DTX bits are grouped regularly into DTX items with length of 1/2 symbol size (2 bits in case of 16QAM). And the DTX items are dispersed to the whole frame.

- (2) DTX items with length of 1/2 symbol size are placed to the 3<sup>rd</sup> and 4<sup>th</sup> bit of symbols.

- (3) By exchanging the DTX bits to "0,0", the symbols with DTX bits can be mapped to the most inner points of the constellation as demonstrated in Figure 8.

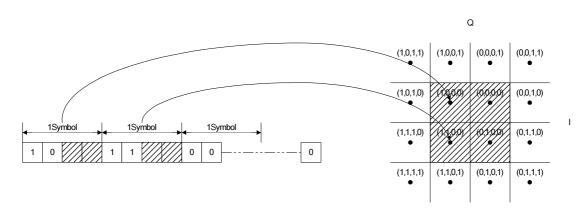

- In case of 64QAM, the DTX grouping and mapping regulation is as follows:

- (1) As shown in Figure 3 and Figure 5, necessary DTX bits are grouped regularly into DTX items with average length of 1/2 symbol size (4bits and 2bits in turn in case of 64QAM). And the DTX items are dispersed to the whole frame.

- (2) For each pair of 4bits and 2bits DTX, the 4bits are inserted into 3<sup>rd</sup> 6<sup>th</sup> bits of one symbol, and the 2bits are inserted into 3<sup>rd</sup> 4<sup>th</sup> bits of another symbol.

- (3) Exchanging 2bits DTX to "0,0" and then symbol with 2bits DTX can be mapped to the 16 most inner points of signal constellation. In the same way, exchanging 4bits DTX to "0,0,1,1" and then the symbol with 4bits DTX can be mapped to the 4 most inner points of signal constellation as demonstrated in Figure 10.

Figure Bit sequence and the constellation (16QAM)

Figure9 Proposed DTX method 2 (64QAM)

Figure 10 Bit sequence and the constellation (64QAM)

For summary, in method 1, DTX bits are grouped into DTX symbols with length of one symbol size and then mapped to origin point, so the DTX symbols transmission power can be off which leads to reduction of average transmission power. In method 2, DTX bits are grouped into items with length of 1/2 symbol size, and placed to proper bit location of symbols which results in the DTX inserted symbol corresponds to the most inner points of signal constellation, and symbols with DTX bits are mapped to the most inner points of signal constellation which results in reduction of average transmission power.

### 3 Performance Comparison

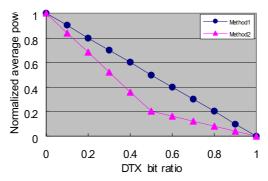

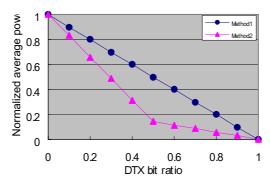

Relation of Average power versus DTX ratio is shown in Figure 11 and 12

Figure 11 Relation of Average power versus DTX ratio (16QAM)

Figure 12 Relation of Average power versus DTX ratio (64QAM)

According to the Figure 11 and 12, we can conclude method 2 has better performance than that of method 1. When DTX bit ratio equals to 0.5, normalized average power is 0.2 in 16QAM, and 0.143 in 64 OAM.

The calculation methodology is shown is appendix A.

#### 4 Conclusion

DTX method for HSDPA is proposed in which two concrete implementation methods are discussed. Our calculation results show that significant average power reduction effect can be achieved by employing the proposed methods. The conclusions are summarized as follows:

- Dummy bit insertion and mapping process is newly proposed after 2<sup>nd</sup> interleaving in order to group DTX dummy bits into items with length of 1 or 1/2 symbol size.

- 2 dummy bit insertion and mapping methods are proposed, one is to group DTX bits into symbols with length of 1 symbol size and map to origin signal point of constellation, and another is to group DTX bits into items with length of 1/2 symbol size and then map to the most inner signal points of constellation.

- Performance comparison in terms of power reduction shows that 1/2 symbol size DTX grouping method is more effective than that of 1 symbol size DTX grouping method.

### 5 Reference

[1]"Physical Layer Aspects of UTRA High Speed Downlink Packet Access" TR25.848V4.0.0, 12A010036

# Appendix Calculation methodology of the average power

### Method 2

(1) 16QAM

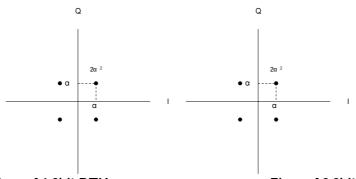

Figure A1 2bit DTX case

Figure A2 2bit DTX case

2bit DTX case(Fig.A1): average power is  $2\alpha^2$

2bit DTX case(Fig.A2): average power is  $2\alpha^2$

Provided that DTX occurrence probability is 1:1,

Normalized average power =  $(0.5*2+0.5*2)\alpha^2/10\alpha^2$

= 0.2

To extension, for any DTX ratio, average power is calculated as follows.

$P_{ave} = 2\beta^*(2/10) + (1-2\beta)^*(10/10)$

; 1≧β≧0.5

$P_{ave} = 2(1-\beta)^*(2/10) + \{1-2(1-\beta)\}^*(0/10)$

; 0.5≧β≧0,

where P<sub>ave</sub> is Normalized average power and βis DTX bit ratio.

## (2) 64QAM

Figure A3 4bit DTX case

Figure A4 2bit DTX case

4bit DTX case(Fig.A3): average power is  $2\alpha^2$

2bit DTX case(Fig.A4): average power is  $10\alpha^2$

Provided that DTX occurrence probability is 1:1,

Normalized average power = (0.5\*2+0.5\*10)  $\alpha^2/42\alpha^2$

= 0.143

To extension, for any DTX ratio, average power is calculated as follows.

$P_{ave} = 2\beta^*(6/42) + (1-2\beta)^*(42/42)$

; 1≧β≧0.5

$P_{ave} = 2(1-\beta)^*(6/42) + \{1-2(1-\beta)\}^*(0/42) \hspace{1cm} ; \hspace{1cm} 0.5 \underline{\geq} \beta \underline{\geq} 0,$

where  $P_{\text{ave}}$  is Normalized average power and  $\;\beta is\; \text{DTX}$  bit ratio.