3GPP TSG-RAN May 21-25, 2001 Busan, Korea

Agenda item: 6

**Source**: Ericsson

Title: Length of HS-DSCH TTI

**Document for:** Discussion and decision

### 1 Introduction

The length of the HS-DSCH TTI has been extensively discussed. At the HSDPA AdHoc, it was concluded that a semi-static TTI should be working assumption for HS-DSCH. However, the set of lengths of the HS-DSCH TTI remains to be decided on. Reference [1] compared two alternatives for the HS-DSCH TTI ( $5 \times T_{slot}$  and  $3 \times T_{slot}$ ) and, in principle concluded that the shorter HS-DSCH TTI ( $3 \times T_{slot}$ ) was preferred. In this paper, we study the impact of the TTI length on available processing time, required soft buffering, and delay. The conclusion is in principle the same as in [1], i.e. as short TTI as possible is preferred. However, in contrast to [1], this paper raises the question if an even shorter TTI, i.e. TTI =  $T_{slot}$  should be considered, taking into account that such a TTI would have a positive impact on e.g. overall HS-DSCH delay.

# 2 Assumptions

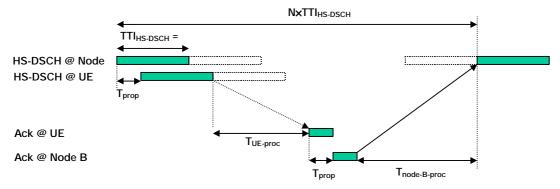

The discussion is based on the following assumptions, see also Figure 1:

- Synchronous N-channel Stop-and-Wait. However, the conclusions should be equally valid also for other Hybrid ARQ schemes.

- The length of the HS-DSCH TTI is  $M \times T_{slot}$  (M $\in$  {1,3,5,15}).

- Propagation delay (uplink and downlink) is independent of the length of the HS-DSCH TTI (rather obvious)

- Length of uplink Hybrid ARQ signalling equal to one slot, i.e. independent of HS-DSCH TTI. This is not necessarily obvious but proposed in e.g. [2].

- Required Node B processing time is independent of the length of the HS-DSCH TTI

Any additional delay due to transmission of HS-DSCH-related downlink signalling prior to the transmission of the HS-DSCH data itself is assumed to be included in the required Node B processing time. Note that this assumes that the time duration of such signalling information is independent of the length of the HS-DSCH TTI, which is not necessarily an obvious assumption.

T<sub>UE-proc</sub>: Time available for UE processing T<sub>Node-B-proc</sub>: Time available for Node B processing

Figure 1

#### 3 Evaluation

From Figure 1, the available processing time (UE processing + Node B processing) is:

$$T_{proc} = T_{UE-proc} + T_{Node-B-proc} = N \times TTI - TTI - 2 \times T_{prop} - T_{slot} = (N \times M - M - 1) \times T_{slot} - 2 \times T_{prop} - T_{slot} = (N \times M - M - 1) \times T_{slot} - 2 \times T_{prop} - T_{slot} = (N \times M - M - 1) \times T_{slot} - 2 \times T_{prop} - T_{slot} = (N \times M - M - 1) \times T_{slot} - 2 \times T_{prop} - T_{slot} = (N \times M - M - 1) \times T_{slot} - 2 \times T_{prop} - T_{slot} = (N \times M - M - 1) \times T_{slot} - 2 \times T_{prop} - T_{slot} = (N \times M - M - 1) \times T_{slot} - 2 \times T_{prop} - T_{slot} = (N \times M - M - 1) \times T_{slot} - 2 \times T_{prop} - T_{slot} = (N \times M - M - 1) \times T_{slot} - 2 \times T_{prop} - T_{slot} = (N \times M - M - 1) \times T_{slot} - 2 \times T_{prop} - T_{slot} = (N \times M - M - 1) \times T_{slot} - 2 \times T_{prop} - T_{slot} = (N \times M - M - 1) \times T_{slot} - 2 \times T_{prop} - T_{slot} - 2 \times T_{prop} - 2 \times T_{pr$$

The required soft buffering for N-channel Stop-and-Wait is proportional to  $N \times TTI$ , i.e. proportional to  $N \times M \times T_{stot}$ . Thus, a constant buffering requirement implies that  $N \times M$  should be constant, i.e.  $N \times M = K$ .

From this, one can conclude that, for a given buffering requirement, the available processing time is

$$T_{proc} = (K - M - 1) \times T_{slot} - 2 \times T_{prop}$$

Thus, for a given buffering requirement, the time available for processing  $T_{proc} = T_{UE-proc} + T_{Node-B-proc}$  increases monotonically as the TTI length is reduced. The increase in available processing time is especially significant if one can make the rather reasonable assumption that the required UE processing time depends on the length of the TTI, in the sense that a shorter TTI leads to shorter required UE processing time.

Alternatively, one can conclude that, for a given available processing time, a shorter TTI implies lower buffering requirements.

An additional and important benefit with a shorter HS-DSCH TTI is the possibility to reduce the Hybrid-ARQ round-trip delay (shorter time between retransmissions), leading to overall reduced HD-DSCH delay.

At should be noted that changing any of the "not necessarily obvious" assumptions above, would just amplify the benefits of a shorter HS-DSCH TTI.

## 4 Conclusions and recommendations

The discussion above has once again confirmed that an as short HS-DSCH TTI as possible is beneficial from a soft-buffering, UE/Node-B-processing, and HS-DSCH delay point-of-view.

From this one can conclude that:

- HS-DSCH TTI at least as short as 3 slots (3×T<sub>slot</sub>) should be supported.

- HS-DSCH TTI as short as one slot (T<sub>slot</sub>) should be considered, especially taking into account the potential for reduced HS-DSCH delay.

- Support for a 10 ms TTI would have a very negative impact on UE buffering requirements. Thus in case 10 ms TTI should be supported, only a fraction of the total HS-DSCH throughput could be given to each UE. This must also be reflected in the definition of HS-DSCH-related UE capabilities. A 10 ms TTI would also have a negative impact on the HS-DSCH delay.

It is proposed that the conclusions listed above are included in [3].

## References

- [1] 3GPP TSG RAN1/RAN2 HSDPA Ad Hoc, April 5-6, 2001, 12A010003, "Further buffer complexity and processing time considerations on HARQ", Nokia

- [2] R1-01-0571 "Uplink signalling for Hybrid ARQ"

- [3] TR 25.855, "High Speed Downlink Packet Access: Overall UTRAN Description"