|                               | N WG1 Meeting#18<br>Jan 15~18, 2001                                                                                                                                                                                                                                                                       | R1-01-0181                                                                                                                                                                       |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2001011, 0071,                | CHANGE REQUEST                                                                                                                                                                                                                                                                                            | CR-Formv3                                                                                                                                                                        |

| £                             | 25.221 CR CR-Num ≤ rev - ≤ C                                                                                                                                                                                                                                                                              | urrent version: 3.4.0                                                                                                                                                            |

| For <u><b>HELP</b></u> on     | using this form, see bottom of this page or look at the p                                                                                                                                                                                                                                                 | op-up text over the 🗷 symbols.                                                                                                                                                   |

| Proposed change               | e affects: 🗷 (U)SIM ME/UE X Radio Acce                                                                                                                                                                                                                                                                    | ess Network X Core Network                                                                                                                                                       |

| Title:                        | CR for TS25.221 regarding the 1.28 Mcps TDD                                                                                                                                                                                                                                                               |                                                                                                                                                                                  |

| Source:                       | CWTS/CATT                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                  |

| Work item code: A             | 1.28 Mcps TDD Physical Layer                                                                                                                                                                                                                                                                              | Date: ∡                                                                                                                                                                          |

| Category:                     | ≾ <mark>R</mark>                                                                                                                                                                                                                                                                                          | Pelease: ⊭ REL-4                                                                                                                                                                 |

|                               | Use <u>one</u> of the following categories:  F (essential correction)  A (corresponds to a correction in an earlier release)  B (Addition of feature),  C (Functional modification of feature)  D (Editorial modification)  Detailed explanations of the above categories can be found in 3GPP TR 21.900. | Use <u>one</u> of the following releases:  2 (GSM Phase 2)  R96 (Release 1996)  R97 (Release 1997)  R98 (Release 1998)  R99 (Release 1999)  REL-4 (Release 4)  REL-5 (Release 5) |

| Reason for chang              | NO: ~                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                  |

| Summary of char               |                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                  |

| Consequences if not approved: | &                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                  |

| Clauses affected:             | £                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                  |

| Other specs affected:         | Other core specifications Test specifications O&M Specifications                                                                                                                                                                                                                                          |                                                                                                                                                                                  |

Other comments:

## 2 References

<For clarity, this chapter will currently collect only the references that are needed in addition to the already existing abbreviations. In its last version this chapter has to be modified, so that it includes the revisions with respect to the latest versions of TS25.221.>

## 3 Abbreviations

< For clarity, this chapter will currently collect only the abbreviations that are needed in addition to the already existing abbreviations. In its last version this chapter has to be modified, so that it includes the revisions with respect to the latest versions of TS25.221.>

| MIB          | Master Information Block |

|--------------|--------------------------|

| <u>UpPTS</u> | Uplink Pilot Time Slot   |

| <u>UpPCH</u> | Uplink Pilot Channel     |

| DwPTS        | Downlink Pilot Time Slot |

| DwPCH        | Downlink Pilot Channel   |

## 4 Transport channels

<This section is included in the working CR for completeness only. No changes will be made in this chapter. This chapter can be removed from the CR in its final version.>

# 5 Physical channels for the 3.84 Mcps option

<No changes will be made in this chapter in this CR, only the title has to be changed. >

# 6 Physical channels for the 1.28 Mcps option

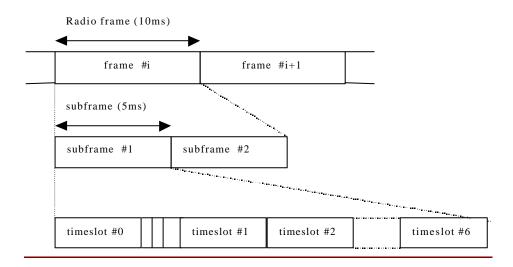

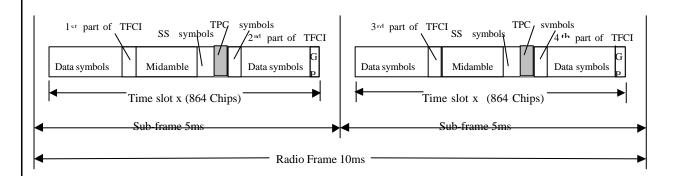

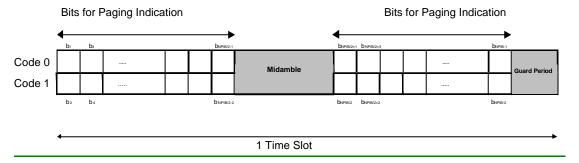

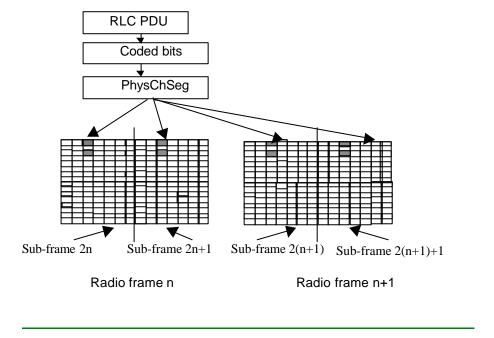

All physical channels take three-layer structure with respect to timeslots, radio frames and system frame numbering (SFN), see [14]. Depending on the resource allocation, the configuration of radio frames or timeslots becomes different. All physical channels need guard symbols in every timeslot. The time slots are used in the sense of a TDMA component to separate different user signals in the time and the code domain. The physical channel signal format for 1.28Mcps TDD is presented in figure [X1].

A physical channel in TDD is a burst, which is transmitted in a particular timeslot within allocated Radio Frames. The allocation can be continuous, i.e. the time slot in every frame is allocated to the physical channel or discontinuous, i.e. the time slot in a subset of all frames is allocated only. A burst is the combination of a data part, a midamble and a guard period. The duration of a burst is one time slot. Several bursts can be transmitted at the same time from one transmitter. In this case, the data part must use different OVSF channelisation codes, but the same scrambling code. The midamble part has to use the same basic midamble code, but can use different midambles.

Figure [X1]: Physical channel signal format for 1.28Mcps TDD option

The data part of the burst is spread with a combination of channelisation code and scrambling code. The channelisation code is a OVSF code, that can have a spreading factor of 1, 2, 4, 8, or 16. The data rate of the physical channel is depending on the used spreading factor of the used OVSF code.

So a physical channel is defined by frequency, timeslot, channelisation code, burst type and Radio Frame allocation The scrambling code and the basic midamble code are broadcast and may be constant within a cell. When a physical channel is established, a start frame is given. The physical channels can either be of infinite duration, or a duration for the allocation can be defined.

### 6.1 Frame structure

The TDMA frame has a duration of 10 ms and is divided into 2 sub-frames of 5ms. The frame structure for each sub-frame in the 10ms frame length is the same.

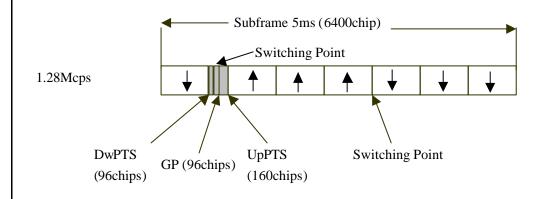

Figure [X2]: Structure of the sub-frame for 1.28Mcps TDD option

Time slot#n (n from 0 to 6): the nth normal time slot, 864 chips duration:

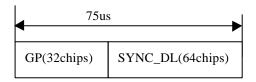

DwPTS: downlink pilot time slot, 96 chips duration:

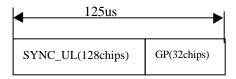

UpPTS: uplink pilot time slot, 160 chips duration:

#### GP: main guard period for TDD operation, 96 chips duration;

In Figure [X2], the total number of normal time slot for uplink and downlink is 7, and the length for each normal time slot is 864 chips duration. Among the 7 normal time slot, time slot#0 is always allocated as downlink while time slot#1 is always allocated as uplink. The time slots for the uplink and the downlink are separated by switching points. Between the downlink time slots and uplink time slots, the special period is the switching point to separate the uplink and downlink. In each sub-frame of 5ms for 1.28Mcps option, there are two switching points (uplink to downlink and vice versa).

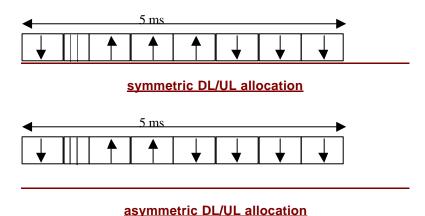

Using the above frame structure, the 1.28Mcps TDD option can operate on both symmetric and asymmetric mode by properly configuring the number of downlink and uplink time slots. In any configuration at least one time slot (time slot#0) has to be allocated for the downlink and at least one time slot has to be allocated for the uplink (time slot#1).

Examples for symmetric and asymmetric UL/DL allocations are given in figure [X3].

Figure [X3]: 1.28Mcps TDD sub-frame structure examples

## 6.2 Dedicated physical channel (DPCH)

The DCH as described in subclause 4.1 'Dedicated transport channels' is mapped onto the dedicated physical channel.

## 6.2.1 Spreading

Spreading is applied to the data part of the physical channels and consists of two operations. The first is the channelisation operation, which transforms every data symbol into a number of chips, thus increasing the bandwidth of the signal. The number of chips per data symbol is called the Spreading Factor (SF). The second operation is the scrambling operation, where a scrambling code is applied to the spread signal. Details on channelisation and scrambling operation can be found in [8].

#### 6.2.1.1 Spreading for Downlink Physical Channels

Downlink physical channels shall use SF = 16. Multiple parallel physical channels can be used to support higher data rates. These parallel physical channels shall be transmitted using different channelisation codes, see [8]. These codes with SF = 16 are generated as described in [8].

Operation with a single code with spreading factor 1 is possible for the downlink physical channels.

#### 6.2.1.2 Spreading for Uplink Physical Channels

The range of spreading factor that may be used for uplink physical channels shall range from 16 down to 1.

For multicode transmission a UE shall use a maximum of two physical channels per timeslot simultaneously. These two parallel physical channels shall be transmitted using different channelisation codes, see [8].

### 6.2.2 Burst Format Types

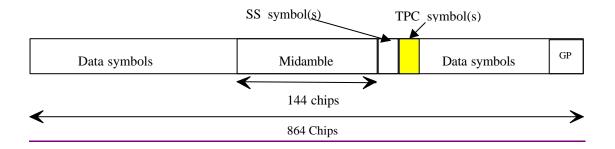

A normal burst consists of two data symbol fields, a midamble of 144 chips and a guard period. The data fields of the burst are 352 chips long. The corresponding number of symbols depends on the spreading factor, as indicated in table X1 below. The guard period is 16 chip periods long.

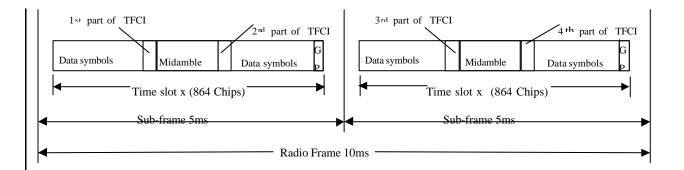

The burst typeformat is shown in Figure X1. The contents of the normal burst fields is described in table X2.

Table X1: number of symbols per data field in a normal burst

| Spreading factor (Q) | Number of symbols (N) per data field in Burst |

|----------------------|-----------------------------------------------|

| <u>1</u>             | <u>352</u>                                    |

| <u>2</u>             | <u>176</u>                                    |

| <u>4</u>             | <u>88</u>                                     |

| <u>8</u>             | <u>44</u>                                     |

| <u>16</u>            | <u>22</u>                                     |

Table X2: The contents of the normal burst type format fields

| Chip number<br>(CN) | Length of field in chips | <u>Length of field in</u><br><u>symbols</u> | Contents of field |

|---------------------|--------------------------|---------------------------------------------|-------------------|

| <u>0-351</u>        | <u>352</u>               | cf table 1                                  | Data symbols      |

| <u>352-495</u>      | <u>144</u>               | <u> </u>                                    | <u>Midamble</u>   |

| 496-847             | <u>352</u>               | cf table 1                                  | Data symbols      |

| <u>848-863</u>      | <u>16</u>                | <u>=</u>                                    | Guard period      |

| Data symbols<br>352 chips | Midamble<br>144 chips | Data symbols<br>352 chips | GP<br>16<br>CP |

|---------------------------|-----------------------|---------------------------|----------------|

| 4                         | 864*T <sub>c</sub>    |                           | _              |

Figure X1: Burst structure of the normal burst typeformat (GP denotes the guard period and CP the chip periods)

#### 6.2.2.1 Transmission of TFCI

The normal burst type format provides the possibility for transmission of TFCI in uplink and downlink.

The transmission of TFCI is negotiated at call setup and can be re-negotiated during the call. For each CCTrCH it is indicated by higher layer signalling, which TFCI format is applied. Additionally for each allocated timeslot it is signalled individually whether that timeslot carries the TFCI or not. If a time slot contains the TFCI, then it is always transmitted using the first allocated channelisation code in the timeslot, according to the order in the higher layer allocation message.

The transmission of TFCI is done in the data parts of the respective physical channel, this means TFCI and data bits are subject to the same spreading procedure as depicted in [8]. Hence the midamble structure and length is not changed.

The encoded TFCI symbols are equally distributed between the two subframes and the respective data fields. The TFCI information is to be transmitted possibly either directly adjacent to the midambleor after the SS and TPC symbols. Figure [X] shows the position of the TFCI in a traffic burst, if neither SS nor TPC are transmitted. Figure [Y] shows the position of the TFCI in a traffic burst, if SS and TPC are transmitted.

Figure X: Position of TFCI information in the traffic burst in case of no TPC and SS in 1.28 Mcps TDD

Figure Y:Position of TFCI information in the traffic burst in case of TPC and SS in 1.28 Mcps TDD

#### 6.2.2.2 Transmission of TPC

The burst type for dedicated channels provides the possibility for transmission of TPC in uplink and downlink.

The transmission of TPC is done in the data parts of the traffic burst. Hence the midamble structure and length is not changed. The TPC information is to be transmitted directly after the SS information, which is transmitted after the midamble. Figure XX shows the position of the TPC command in a traffic burst.

For every user the TPC information is to be transmitted at least once per 5ms sub-frame. If applied, transmission of TPC is done in the data parts of the traffic burst and it can be transmitted using the first allocated channelisation code and the first allocated timeslot (according to the order in the higher layer allocation message). Other allocations (more than one TPC transmission in one sub-frame) of TPC are also possible. The TPC is spread with the same spreading factor (SF) and spreading code as the data parts of the respective physical channel.

Figure X: TPC information in a burst in downlink and uplink

For the number of layer 1 symbols per channelisation code there are 3 possibilities configurable for each channelisation code during the call setup:

- ?? one SS and one TPC symbol

- ?? no SS and no TPC symbols

- ?? 16/SF SS and 16/SF TPC symbols

So, in case 3, when SF=1, there are 16 TPC symbols which correspond to 32 bits (for OPSK) and 48 bits (for 8PSK).

In the following the uplink is described only. For the description of the downlink, downlink (DL) and uplink (UL) have to be interchanged.

Each of the TPC symbols for uplink power control in the DL will be associated with an UL time slot and an UL CCTrCH pair. This association varies with

- ?? the number of allocated UL time slots and UL CCTrCHs on these time slots (time slot and CCTrCH pair) and

- ?? the allocated TPC symbols in the DL.

In case a UE has

more than one channelisation code

and/or

channelisation codes being of lower spreading factor than 16 and using 16/SF SS and 16/SF TPC symbols.

the TPC commands for each ULtime slot CCTrCH pair (all channelisation codes on that time slot belonging to the same time slot and CCTrCH pair have the same TPC command) will be distributed to the following rules:

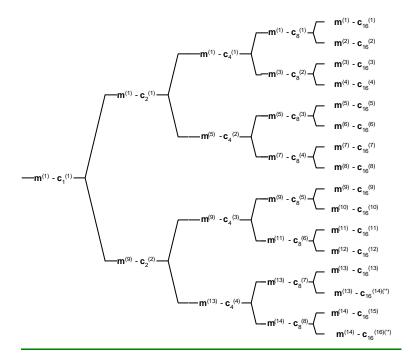

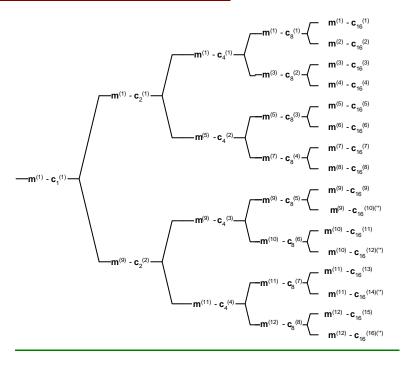

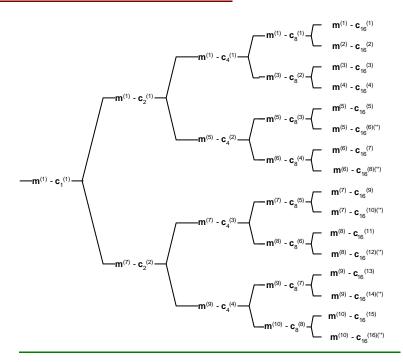

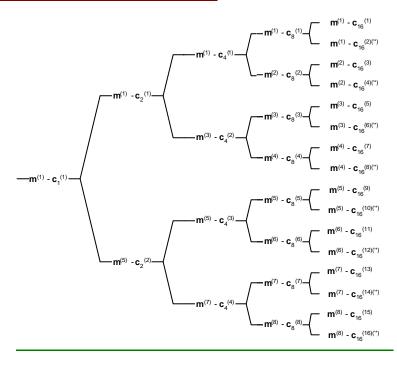

- 1. The ULtime slots and CCTrCH pairs the TPC commands are intended for will be numbered form the first to the last ULtime slot and CCTrCH pair allocated to the regarded UE (starting with 0). The number of a time slot and CCTrCH pair is smaller then the number of another time slot and CCTrCH pair within the same time slot if its spreading code with the lowest SC number according to the following table has a lower SC number then the spreading code with the lowest SC number of the other time slot and CCTrCH pair.

- 2. The commanding TPC symbols on all DLCCTrCHs allocated to one UE are numbered consecutively starting with zero according to the following rules:

- a) The numbers of the TPC commands of a regarded DL time slot are lower than those of DL time slots being transmitted after that time slot

- b) Within a DL time slot the numbers of the TPC commands of a regarded channelisation code are lower than those of channelisation codes having a higher spreading code number

The spreading code number is defined by the following table: (see TS 25.223)

|           | 1         |                                               |

|-----------|-----------|-----------------------------------------------|

| SC number | SF (Q)    | Walsh code number (k)                         |

| 0         | <u>16</u> | $\frac{\mathbf{c}_{Q?16}^{(k?1)}}{}$          |

|           | <u></u>   |                                               |

| <u>15</u> | <u>16</u> | $\frac{\mathbf{c}_{Q?16}^{(k?16)}}{}$         |

| <u>16</u> | 8         | $\frac{\mathbf{c}_{Q?8}^{(k?1)}}{}$           |

|           |           |                                               |

| <u>23</u> | 8         | $\frac{\mathbf{c}_{Q^{?8}}^{(k?8)}}{}$        |

| <u>24</u> | 4         | $\frac{\mathbf{c}_{Q?4}^{(k?1)}}{}$           |

|           |           |                                               |

| <u>27</u> | 4         | $\frac{\mathbf{c}_{Q?4}^{(k?4)}}{}$           |

| <u>28</u> | 2         | $\frac{\mathbf{c}_{Q?2}^{(k?1)}}{}$           |

| <u>29</u> | 2         | $\frac{\mathbf{c}_{\mathcal{Q}?2}^{(k?2)}}{}$ |

| <u>30</u> | 1         | $\frac{\mathbf{c}_{Q?1}^{(k?1)}}{}$           |

Note: Spreading factors 2-8 are not used in DL

c) Within a channelisation code numbers of the TPC commands are lower than those of TPC commands being transmitted after that time

The following equation is used to determine the UL time slot which is controlled by the regarded TPC symbol in the DL:

$$UL_{pos}$$

? (SFN'? $N_{UL\_TPC symbols}$  ?  $TPC_{DLpos}$ )  $mod(N_{UL slot})$  .

where

<u>UL<sub>pos</sub> is the number of the controlled uplink time slot and CCTrCH pairs.</u>

SFN' is the system frame number counting the sub-frames. The system frame number of the radio frames (SFN) can be derived from SFN' by

SFN=SFN' div 2, where div is the reminder free division operation.

$\underline{N}_{UL\_PC symbols}$  is the number of UL TPC symbols in a sub-frame.

<u>TPC<sub>DLpos</sub> is the number of the regarded UL TPC symbol in the DL within the sub-frame.</u>

N<sub>ULslot</sub> is the number of UL slots and CCTrCH pairs in a frame.

In Annex G two examples of the association of TPC commands to time slots and CCTrCH pairs are shown,

#### **Coding of TPC:**

The relationship between the TPC Bits and the transmitter power control command for QPSK is the same as in the 3.84Mcps TDD cf. [5.2.2.5 'Transmission of TPC'].

The relationship between the TPC Bits and the transmitter power control command for 8PSK is given in table [XX]

**Table XX: TPC Bit Pattern for 8PSK**

| TPC           | TPC Bit Pattern | <u>Meaning</u>    |

|---------------|-----------------|-------------------|

| <u>'Down'</u> | <u>000</u>      | Decrease Tx Power |

| <u>'Up'</u>   | <u>110</u>      | Increase Tx Power |

#### 6.2.2.3 Transmission of SS

#### Coding of SS for QPSK:

The SS command is an identifier sent in downlink transmission only, to instruct the UE whether the synchronisation shift has to be increased or decreased by k/8 Tc or has to remain unchanged. The length of the SS command is one symbol. The coding of the SS command is shown in table XX.

The default value of k (1-8) is broadcast in the BCH. The value of k can also be adjusted during call setup or readjusted during the call.

Note: The smallest step for the SS signalled by the UTRAN is 1/8 Tc. For the UE capabilities regarding the SS adjustment of the UE it is suggested to set the tolerance for the executed command to be [1/9;1/7] Tc.

Table XX: Coding of the SS for QPSK

| <u>SS</u>           | SS Bits   | <u>Meaning</u>                           |

|---------------------|-----------|------------------------------------------|

| <u>'Down'</u>       | <u>00</u> | Decrease synchronisation shift by k/8 Tc |

| <u>'Up'</u>         | <u>11</u> | Increase synchronisation shift by k/8 Tc |

| <u>'Do nothing'</u> | <u>01</u> | No change                                |

#### Coding of SS for 8PSK:

The SS command is an identifier sent in downlink transmission only, to instruct the UE whether the synchronisation shift has to be increased or decreased by k/8 Tc or has to stay unchanged. The length of the SS command is one symbol. The coding of the SS command is shown in table XXX.

The default value of k (1-8) is broadcast in the BCH. The value of k can also be adjusted during call setup or readjusted during the call.

Note: The smallest step for the SS signalled by the UTRAN is 1/8 Tc. For the UE capabilities regarding the SS adjustment of the UE it is suggested to set the tolerance for the executed command to be [1/9:1/7] Tc.

Table XXX: Coding of the SS for 8PSK

| <u>ss</u>     | SS Bits    | <u>Meaning</u>                           |

|---------------|------------|------------------------------------------|

| <u>'Down'</u> | <u>000</u> | Decrease synchronisation shift by k/8 Tc |

| <u>'Up'</u>   | <u>110</u> | Increase synchronisation shift by k/8 Tc |

| 'Do nothing'  | <u>011</u> | No change                                |

## 6.2.2.4 Timeslot formats

## 6.2.2.4.1 time slot formats for QPSK

## 6.2.2.4.1.1 Downlink timeslot formats

Table : Time slot formats for the Downlink

| Slot Format<br># | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | Nss & NTPC | Bits/slot | N <sub>Data/Slot</sub> (bits) | Ndata/data<br>field(1) (bits) | Ndata/data<br>field(2) (bits) |

|------------------|---------------------|-------------------------------|--------------------------|------------|-----------|-------------------------------|-------------------------------|-------------------------------|

| <u>O</u>         | <u>16</u>           | <u>144</u>                    | <u>O</u>                 | 0 & 0      | <u>88</u> | <u>88</u>                     | <u>44</u>                     | <u>44</u>                     |

| 1                | <u>16</u>           | <u>144</u>                    | <u>4</u>                 | 0 & 0      | <u>88</u> | <u>86</u>                     | <u>42</u>                     | <u>44</u>                     |

| 2                | <u>16</u>           | 144                           | 8                        | 0 & 0      | <u>88</u> | <u>84</u>                     | <u>42</u>                     | <u>42</u>                     |

| 3                | <u>16</u>           | <u>144</u>                    | <u>16</u>                | 0 & 0      | <u>88</u> | <u>80</u>                     | <u>40</u>                     | <u>40</u>                     |

| 4                | <u>16</u>           | <u>144</u>                    | <u>32</u>                | 0 & 0      | <u>88</u> | <u>72</u>                     | <u>36</u>                     | <u>36</u>                     |

| <u>5</u>         | <u>16</u>           | <u>144</u>                    | <u>O</u>                 | 2 & 2      | <u>88</u> | <u>84</u>                     | <u>44</u>                     | <u>40</u>                     |

| <u>6</u>         | <u>16</u>           | <u>144</u>                    | 4                        | 2 & 2      | <u>88</u> | <u>82</u>                     | <u>42</u>                     | <u>40</u>                     |

| 7                | <u>16</u>           | <u>144</u>                    | 8                        | 2 & 2      | <u>88</u> | <u>80</u>                     | <u>42</u>                     | <u>38</u>                     |

| 8                | <u>16</u>           | 144                           | <u>16</u>                | 2 & 2      | <u>88</u> | <u>76</u>                     | <u>40</u>                     | <u>36</u>                     |

| 9                | <u>16</u>           | <u>144</u>                    | <u>32</u>                | 2 & 2      | 88        | <u>68</u>                     | <u>36</u>                     | <u>32</u>                     |

| Slot Format # | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | Nss & NTPC         | Bits/slot   | N <sub>Data/Slot</sub> (bits) | Ndata/data<br>field(1) (bits) | Ndata/data<br>field(2) (bits) |

|---------------|---------------------|-------------------------------|--------------------------|--------------------|-------------|-------------------------------|-------------------------------|-------------------------------|

| <u>10</u>     | 1                   | <u>144</u>                    | <u>0</u>                 | 0 & 0              | <u>1408</u> | <u>1408</u>                   | <u>704</u>                    | <u>704</u>                    |

| 11            | 1                   | <u>144</u>                    | <u>4</u>                 | 0 & 0              | <u>1408</u> | <u>1406</u>                   | <u>702</u>                    | <u>704</u>                    |

| <u>12</u>     | 1                   | <u>144</u>                    | <u>8</u>                 | 0 & 0              | <u>1408</u> | <u>1404</u>                   | <u>702</u>                    | <u>702</u>                    |

| <u>13</u>     | 1                   | <u>144</u>                    | <u>16</u>                | 0 & 0              | <u>1408</u> | <u>1400</u>                   | 700                           | <u>700</u>                    |

| 14            | 1                   | <u>144</u>                    | <u>32</u>                | 0 & 0              | <u>1408</u> | <u>1392</u>                   | <u>696</u>                    | <u>696</u>                    |

| <u>15</u>     | 1                   | <u>144</u>                    | <u>0</u>                 | 2 & 2              | <u>1408</u> | <u>1404</u>                   | <u>704</u>                    | <u>700</u>                    |

| <u>16</u>     | 1                   | <u>144</u>                    | <u>4</u>                 | 2 & 2              | <u>1408</u> | <u>1402</u>                   | 702                           | <u>700</u>                    |

| <u>17</u>     | 1                   | <u>144</u>                    | <u>8</u>                 | 2 & 2              | <u>1408</u> | <u>1400</u>                   | <u>702</u>                    | <u>698</u>                    |

| <u>18</u>     | 1                   | <u>144</u>                    | <u>16</u>                | 2 & 2              | <u>1408</u> | <u>1396</u>                   | 700                           | <u>696</u>                    |

| <u>19</u>     | 1                   | <u>144</u>                    | <u>32</u>                | 2 & 2              | <u>1408</u> | <u>1388</u>                   | <u>696</u>                    | <u>692</u>                    |

| 20            | 1                   | <u>144</u>                    | <u>0</u>                 | <u>32 &amp; 32</u> | <u>1408</u> | <u>1344</u>                   | <u>704</u>                    | <u>640</u>                    |

| <u>21</u>     | 1                   | <u>144</u>                    | <u>4</u>                 | <u>32 &amp; 32</u> | <u>1408</u> | <u>1342</u>                   | <u>702</u>                    | <u>640</u>                    |

| <u>22</u>     | 1                   | 144                           | <u>8</u>                 | <u>32 &amp; 32</u> | <u>1408</u> | <u>1340</u>                   | 702                           | <u>638</u>                    |

| <u>23</u>     | 1                   | <u>144</u>                    | <u>16</u>                | <u>32 &amp; 32</u> | <u>1408</u> | <u>1336</u>                   | 700                           | <u>636</u>                    |

| <u>24</u>     | 1                   | 144                           | <u>32</u>                | 32 & 32            | <u>1408</u> | <u>1328</u>                   | <u>696</u>                    | 632                           |

## 6.2.2.4.1.2 Uplink timeslot formats

Table: Time slot formats for the Uplink

| Slot Format # | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | Nss & NTPC | Bits/slot  | N <sub>Data/Slot</sub> (bits) | Ndata/data<br>field(1) (bits) | Ndata/data<br>field(2) (bits) |

|---------------|---------------------|-------------------------------|--------------------------|------------|------------|-------------------------------|-------------------------------|-------------------------------|

| <u>O</u>      | <u>16</u>           | <u>144</u>                    | <u>0</u>                 | 0 & 0      | <u>88</u>  | <u>88</u>                     | <u>44</u>                     | <u>44</u>                     |

| 1             | <u>16</u>           | <u>144</u>                    | 4                        | 0 & 0      | <u>88</u>  | <u>86</u>                     | <u>42</u>                     | <u>44</u>                     |

| 2             | <u>16</u>           | <u>144</u>                    | 8                        | 0 & 0      | <u>88</u>  | <u>84</u>                     | <u>42</u>                     | <u>42</u>                     |

| 3             | <u>16</u>           | <u>144</u>                    | <u>16</u>                | 0 & 0      | <u>88</u>  | <u>80</u>                     | <u>40</u>                     | <u>40</u>                     |

| 4             | <u>16</u>           | <u>144</u>                    | <u>32</u>                | 0 & 0      | <u>88</u>  | <u>72</u>                     | <u>36</u>                     | <u>36</u>                     |

| 5             | <u>16</u>           | <u>144</u>                    | <u>O</u>                 | 2 & 2      | <u>88</u>  | <u>84</u>                     | <u>44</u>                     | <u>40</u>                     |

| 6             | <u>16</u>           | <u>144</u>                    | 4                        | 2 & 2      | <u>88</u>  | <u>82</u>                     | <u>42</u>                     | <u>40</u>                     |

| Z             | <u>16</u>           | <u>144</u>                    | 8                        | 2 & 2      | <u>88</u>  | <u>80</u>                     | <u>42</u>                     | <u>38</u>                     |

| 8             | <u>16</u>           | <u>144</u>                    | <u>16</u>                | 2 & 2      | <u>88</u>  | <u>76</u>                     | <u>40</u>                     | <u>36</u>                     |

| 9             | <u>16</u>           | <u>144</u>                    | <u>32</u>                | 2 & 2      | <u>88</u>  | <u>68</u>                     | <u>36</u>                     | <u>32</u>                     |

| <u>10</u>     | <u>8</u>            | <u>144</u>                    | <u>0</u>                 | 0 & 0      | <u>176</u> | <u>176</u>                    | <u>88</u>                     | <u>88</u>                     |

| 11            | <u>8</u>            | <u>144</u>                    | <u>4</u>                 | 0 & 0      | <u>176</u> | <u>174</u>                    | <u>86</u>                     | <u>88</u>                     |

| <u>12</u>     | <u>8</u>            | <u>144</u>                    | <u>8</u>                 | 0 & 0      | <u>176</u> | <u>172</u>                    | <u>86</u>                     | <u>86</u>                     |

| 13            | <u>8</u>            | <u>144</u>                    | <u>16</u>                | 0 & 0      | <u>176</u> | <u>168</u>                    | <u>84</u>                     | <u>84</u>                     |

| Slot Format # | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | Nss & NTPC       | Bits/slot  | N <sub>Data/Slot</sub> (bits) | Ndata/data<br>field(1) (bits) | Ndata/data<br>field(2) (bits) |

|---------------|---------------------|-------------------------------|--------------------------|------------------|------------|-------------------------------|-------------------------------|-------------------------------|

| 14            | <u>8</u>            | <u>144</u>                    | <u>32</u>                | 0 & 0            | <u>176</u> | <u>160</u>                    | <u>80</u>                     | <u>80</u>                     |

| <u>15</u>     | <u>8</u>            | <u>144</u>                    | <u>0</u>                 | 2 & 2            | <u>176</u> | <u>172</u>                    | <u>88</u>                     | <u>84</u>                     |

| <u>16</u>     | <u>8</u>            | <u>144</u>                    | 4                        | 2 & 2            | <u>176</u> | <u>170</u>                    | <u>86</u>                     | <u>84</u>                     |

| <u>17</u>     | <u>8</u>            | <u>144</u>                    | <u>8</u>                 | 2 & 2            | <u>176</u> | <u>168</u>                    | <u>86</u>                     | <u>82</u>                     |

| <u>18</u>     | <u>8</u>            | <u>144</u>                    | <u>16</u>                | 2 & 2            | <u>176</u> | <u>164</u>                    | <u>84</u>                     | <u>80</u>                     |

| <u>19</u>     | <u>8</u>            | <u>144</u>                    | <u>32</u>                | <u>2 &amp; 2</u> | <u>176</u> | <u>156</u>                    | <u>80</u>                     | <u>76</u>                     |

| <u>20</u>     | 8                   | <u>144</u>                    | <u>O</u>                 | <u>4 &amp; 4</u> | <u>176</u> | <u>168</u>                    | <u>88</u>                     | <u>80</u>                     |

| <u>21</u>     | 8                   | 144                           | 4                        | 4 & 4            | <u>176</u> | <u>166</u>                    | <u>86</u>                     | <u>80</u>                     |

| <u>22</u>     | 8                   | <u>144</u>                    | 8                        | 4 & 4            | <u>176</u> | <u>164</u>                    | <u>86</u>                     | <u>78</u>                     |

| 23            | <u>8</u>            | <u>144</u>                    | <u>16</u>                | 4 & 4            | <u>176</u> | <u>160</u>                    | <u>84</u>                     | <u>76</u>                     |

| <u>24</u>     | <u>8</u>            | <u>144</u>                    | <u>32</u>                | 4 & 4            | <u>176</u> | <u>152</u>                    | <u>80</u>                     | <u>72</u>                     |

| <u>25</u>     | <u>4</u>            | <u>144</u>                    | <u>O</u>                 | 0 & 0            | <u>352</u> | <u>352</u>                    | <u>176</u>                    | <u>176</u>                    |

| <u>26</u>     | <u>4</u>            | <u>144</u>                    | 4                        | 0 & 0            | <u>352</u> | <u>350</u>                    | <u>174</u>                    | <u>176</u>                    |

| <u>27</u>     | <u>4</u>            | <u>144</u>                    | <u>8</u>                 | 0 & 0            | <u>352</u> | <u>348</u>                    | <u>174</u>                    | <u>174</u>                    |

| <u>28</u>     | <u>4</u>            | <u>144</u>                    | <u>16</u>                | 0 & 0            | <u>352</u> | <u>344</u>                    | <u>172</u>                    | <u>172</u>                    |

| <u>29</u>     | <u>4</u>            | <u>144</u>                    | <u>32</u>                | 0 & 0            | <u>352</u> | <u>336</u>                    | <u>168</u>                    | <u>168</u>                    |

| 30            | <u>4</u>            | <u>144</u>                    | <u>0</u>                 | 2 & 2            | <u>352</u> | <u>348</u>                    | <u>176</u>                    | <u>172</u>                    |

| Slot Format # | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | Nss & NTPC       | Bits/slot  | N <sub>Data/Slot</sub> (bits) | Ndata/data<br>field(1) (bits) | Ndata/data<br>field(2) (bits) |

|---------------|---------------------|-------------------------------|--------------------------|------------------|------------|-------------------------------|-------------------------------|-------------------------------|

| <u>31</u>     | <u>4</u>            | <u>144</u>                    | <u>4</u>                 | 2 & 2            | <u>352</u> | <u>346</u>                    | <u>174</u>                    | <u>172</u>                    |

| <u>32</u>     | <u>4</u>            | <u>144</u>                    | <u>8</u>                 | <u>2 &amp; 2</u> | <u>352</u> | <u>344</u>                    | <u>174</u>                    | <u>170</u>                    |

| <u>33</u>     | <u>4</u>            | <u>144</u>                    | <u>16</u>                | 2 & 2            | <u>352</u> | <u>340</u>                    | <u>172</u>                    | <u>168</u>                    |

| <u>34</u>     | <u>4</u>            | <u>144</u>                    | <u>32</u>                | 2 & 2            | <u>352</u> | <u>332</u>                    | <u>168</u>                    | <u>164</u>                    |

| <u>35</u>     | 4                   | <u>144</u>                    | <u>O</u>                 | 8 & 8            | <u>352</u> | <u>336</u>                    | <u>176</u>                    | <u>160</u>                    |

| <u>36</u>     | <u>4</u>            | <u>144</u>                    | 4                        | 8 & 8            | <u>352</u> | <u>334</u>                    | <u>174</u>                    | <u>160</u>                    |

| <u>37</u>     | 4                   | <u>144</u>                    | 8                        | 8 & 8            | <u>352</u> | <u>332</u>                    | <u>174</u>                    | <u>158</u>                    |

| 38            | <u>4</u>            | <u>144</u>                    | <u>16</u>                | 8 & 8            | <u>352</u> | <u>328</u>                    | <u>172</u>                    | <u>156</u>                    |

| <u>39</u>     | 4                   | <u>144</u>                    | <u>32</u>                | 8 & 8            | <u>352</u> | <u>320</u>                    | <u>168</u>                    | <u>152</u>                    |

| <u>40</u>     | 2                   | <u>144</u>                    | <u>0</u>                 | 0 & 0            | <u>704</u> | <u>704</u>                    | <u>352</u>                    | <u>352</u>                    |

| 41            | 2                   | <u>144</u>                    | 4                        | 0 & 0            | <u>704</u> | <u>702</u>                    | <u>350</u>                    | <u>352</u>                    |

| <u>42</u>     | 2                   | <u>144</u>                    | 8                        | 0 & 0            | <u>704</u> | <u>700</u>                    | <u>350</u>                    | <u>350</u>                    |

| <u>43</u>     | 2                   | <u>144</u>                    | <u>16</u>                | 0 & 0            | <u>704</u> | <u>696</u>                    | <u>348</u>                    | <u>348</u>                    |

| 44            | 2                   | <u>144</u>                    | <u>32</u>                | 0 & 0            | <u>704</u> | <u>688</u>                    | <u>344</u>                    | <u>344</u>                    |

| <u>45</u>     | 2                   | <u>144</u>                    | <u>0</u>                 | 2 & 2            | <u>704</u> | <u>700</u>                    | <u>352</u>                    | <u>348</u>                    |

| <u>46</u>     | 2                   | <u>144</u>                    | <u>4</u>                 | 2 & 2            | <u>704</u> | <u>698</u>                    | <u>350</u>                    | <u>348</u>                    |

| 47            | <u>2</u>            | <u>144</u>                    | <u>8</u>                 | 2 & 2            | <u>704</u> | <u>696</u>                    | <u>350</u>                    | <u>346</u>                    |

| Slot Format # | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | Nss & NTPC         | Bits/slot   | N <sub>Data/Slot</sub> (bits) | Ndata/data<br>field(1) (bits) | Ndata/data<br>field(2) (bits) |

|---------------|---------------------|-------------------------------|--------------------------|--------------------|-------------|-------------------------------|-------------------------------|-------------------------------|

| 48            | 2                   | <u>144</u>                    | <u>16</u>                | 2 & 2              | <u>704</u>  | <u>692</u>                    | <u>348</u>                    | <u>344</u>                    |

| <u>49</u>     | 2                   | <u>144</u>                    | <u>32</u>                | 2 & 2              | <u>704</u>  | <u>684</u>                    | 344                           | <u>340</u>                    |

| <u>50</u>     | 2                   | <u>144</u>                    | <u>0</u>                 | <u>16 &amp; 16</u> | <u>704</u>  | <u>672</u>                    | <u>352</u>                    | <u>320</u>                    |

| <u>51</u>     | 2                   | <u>144</u>                    | 4                        | <u>16 &amp; 16</u> | <u>704</u>  | <u>670</u>                    | <u>350</u>                    | <u>320</u>                    |

| <u>52</u>     | 2                   | <u>144</u>                    | <u>8</u>                 | <u>16 &amp; 16</u> | <u>704</u>  | <u>668</u>                    | <u>350</u>                    | <u>318</u>                    |

| <u>53</u>     | 2                   | <u>144</u>                    | <u>16</u>                | <u>16 &amp; 16</u> | <u>704</u>  | <u>664</u>                    | <u>348</u>                    | <u>316</u>                    |

| <u>54</u>     | 2                   | <u>144</u>                    | <u>32</u>                | <u>16 &amp; 16</u> | <u>704</u>  | <u>656</u>                    | <u>344</u>                    | <u>312</u>                    |

| <u>55</u>     | 1                   | <u>144</u>                    | <u>0</u>                 | 0 & 0              | <u>1408</u> | 1408                          | <u>704</u>                    | <u>704</u>                    |

| <u>56</u>     | <u>1</u>            | <u>144</u>                    | <u>4</u>                 | 0 & 0              | <u>1408</u> | <u>1406</u>                   | <u>702</u>                    | <u>704</u>                    |

| <u>57</u>     | 1                   | <u>144</u>                    | <u>8</u>                 | 0 & 0              | <u>1408</u> | <u>1404</u>                   | <u>702</u>                    | <u>702</u>                    |

| <u>58</u>     | 1                   | <u>144</u>                    | <u>16</u>                | 0 & 0              | <u>1408</u> | 1400                          | <u>700</u>                    | <u>700</u>                    |

| <u>59</u>     | 1                   | <u>144</u>                    | <u>32</u>                | 0 & 0              | <u>1408</u> | <u>1392</u>                   | <u>696</u>                    | <u>696</u>                    |

| <u>60</u>     | 1                   | <u>144</u>                    | <u>O</u>                 | 2 & 2              | <u>1408</u> | <u>1404</u>                   | <u>704</u>                    | 700                           |

| <u>61</u>     | 1                   | <u>144</u>                    | <u>4</u>                 | 2 & 2              | <u>1408</u> | 1402                          | <u>702</u>                    | <u>700</u>                    |

| <u>62</u>     | 1                   | <u>144</u>                    | <u>8</u>                 | 2 & 2              | <u>1408</u> | 1400                          | <u>702</u>                    | <u>698</u>                    |

| <u>63</u>     | 1                   | <u>144</u>                    | <u>16</u>                | 2 & 2              | <u>1408</u> | <u>1396</u>                   | <u>700</u>                    | <u>696</u>                    |

| <u>64</u>     | 1                   | <u>144</u>                    | <u>32</u>                | 2 & 2              | <u>1408</u> | <u>1388</u>                   | <u>696</u>                    | <u>692</u>                    |

| Slot Format # | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | N <sub>SS</sub> & N <sub>TPC</sub> | Bits/slot   | N <sub>Data/Slot</sub> (bits) | Ndata/data field(1) (bits) | Ndata/data<br>field(2) (bits) |

|---------------|---------------------|-------------------------------|--------------------------|------------------------------------|-------------|-------------------------------|----------------------------|-------------------------------|

| <u>65</u>     | 1                   | <u>144</u>                    | <u>0</u>                 | <u>32 &amp; 32</u>                 | 1408        | 1344                          | <u>704</u>                 | <u>640</u>                    |

| <u>66</u>     | 1                   | <u>144</u>                    | 4                        | <u>32 &amp; 32</u>                 | <u>1408</u> | <u>1342</u>                   | <u>702</u>                 | <u>640</u>                    |

| <u>67</u>     | 1                   | <u>144</u>                    | 8                        | <u>32 &amp; 32</u>                 | <u>1408</u> | <u>1340</u>                   | <u>702</u>                 | <u>638</u>                    |

| <u>68</u>     | 1                   | 144                           | <u>16</u>                | 32 & 32                            | 1408        | <u>1336</u>                   | <u>700</u>                 | <u>636</u>                    |

| <u>69</u>     | 1                   | <u>144</u>                    | <u>32</u>                | <u>32 &amp; 32</u>                 | <u>1408</u> | <u>1328</u>                   | <u>696</u>                 | <u>632</u>                    |

## 6.2.2.4.2 Time slot formats for 8PSK

#### 6.2.2.4.2.1 Downlink timeslot formats

### 6.2.2.4.2.2 Uplink timeslot formats

The Downlink and the Uplink timeslot formats are described together in the following table.

Table: Timeslot formats for 8PSK modulation

| Slot Format # | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | Nss & NTPC         | Bits/slot   | N <sub>Data/Slot</sub> | Ndata/data<br>field(1) (bits) | Ndata/data<br>field(2) (bits) |

|---------------|---------------------|-------------------------------|--------------------------|--------------------|-------------|------------------------|-------------------------------|-------------------------------|

| <u>O</u>      | 1                   | <u>144</u>                    | <u>0</u>                 | 0 & 0              | <u>2112</u> | 2112                   | <u>1056</u>                   | <u>1056</u>                   |

| 1             | 1                   | <u>144</u>                    | <u>6</u>                 | 0 & 0              | <u>2112</u> | <u>2109</u>            | <u>1053</u>                   | <u>1056</u>                   |

| 2             | 1                   | <u>144</u>                    | <u>12</u>                | 0 & 0              | <u>2112</u> | <u>2106</u>            | <u>1053</u>                   | <u>1053</u>                   |

| 3             | 1                   | <u>144</u>                    | <u>24</u>                | 0 & 0              | <u>2112</u> | <u>2100</u>            | <u>1050</u>                   | <u>1050</u>                   |

| 4             | 1                   | <u>144</u>                    | <u>48</u>                | 0 & 0              | <u>2112</u> | 2088                   | <u>1044</u>                   | <u>1044</u>                   |

| <u>5</u>      | 1                   | <u>144</u>                    | <u>O</u>                 | 3 & 3              | <u>2112</u> | <u>2106</u>            | <u>1056</u>                   | <u>1050</u>                   |

| <u>6</u>      | 1                   | <u>144</u>                    | <u>6</u>                 | 3 & 3              | <u>2112</u> | <u>2103</u>            | <u>1053</u>                   | <u>1050</u>                   |

| Z             | 1                   | <u>144</u>                    | <u>12</u>                | 3 & 3              | <u>2112</u> | 2100                   | <u>1053</u>                   | 1047                          |

| 8             | 1                   | <u>144</u>                    | <u>24</u>                | 3 & 3              | <u>2112</u> | 2094                   | <u>1050</u>                   | <u>1044</u>                   |

| 9             | 1                   | <u>144</u>                    | <u>48</u>                | <u>3 &amp; 3</u>   | 2112        | 2082                   | <u>1044</u>                   | <u>1038</u>                   |

| 10            | 1                   | <u>144</u>                    | <u>O</u>                 | 48 & 48            | <u>2112</u> | <u>2016</u>            | <u>1056</u>                   | <u>960</u>                    |

| 11            | 1                   | <u>144</u>                    | <u>6</u>                 | 48 & 48            | <u>2112</u> | 2013                   | <u>1053</u>                   | <u>960</u>                    |

| <u>12</u>     | 1                   | 144                           | <u>12</u>                | <u>48 &amp; 48</u> | <u>2112</u> | 2010                   | <u>1053</u>                   | <u>957</u>                    |

| <u>13</u>     | 1                   | <u>144</u>                    | <u>24</u>                | <u>48 &amp; 48</u> | <u>2112</u> | <u>2004</u>            | <u>1050</u>                   | <u>954</u>                    |

| 14            | 1                   | 144                           | <u>48</u>                | <u>48 &amp; 48</u> | 2112        | <u>1992</u>            | <u>1044</u>                   | 948                           |

| <u>15</u>     | <u>16</u>           | <u>144</u>                    | <u>0</u>                 | 0 & 0              | <u>132</u>  | <u>132</u>             | <u>66</u>                     | <u>66</u>                     |

| Slot Format # | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | Nss & NTPC (bits) | Bits/slot  | N <sub>Data/Slot</sub><br>(bits) | Ndata/data<br>field(1) (bits) | Ndata/data<br>field(2) (bits) |

|---------------|---------------------|-------------------------------|--------------------------|-------------------|------------|----------------------------------|-------------------------------|-------------------------------|

| <u>16</u>     | <u>16</u>           | <u>144</u>                    | <u>6</u>                 | 0 & 0             | <u>132</u> | <u>129</u>                       | <u>63</u>                     | <u>66</u>                     |

| <u>17</u>     | <u>16</u>           | <u>144</u>                    | <u>12</u>                | 0 & 0             | <u>132</u> | <u>126</u>                       | <u>63</u>                     | <u>63</u>                     |

| <u>18</u>     | <u>16</u>           | <u>144</u>                    | <u>24</u>                | 0 & 0             | <u>132</u> | <u>120</u>                       | <u>60</u>                     | <u>60</u>                     |

| <u>19</u>     | <u>16</u>           | <u>144</u>                    | <u>48</u>                | 0 & 0             | <u>132</u> | <u>108</u>                       | <u>54</u>                     | <u>54</u>                     |

| 20            | <u>16</u>           | <u>144</u>                    | <u>0</u>                 | <u>3 &amp; 3</u>  | <u>132</u> | <u>126</u>                       | <u>66</u>                     | <u>60</u>                     |

| <u>21</u>     | <u>16</u>           | <u>144</u>                    | <u>6</u>                 | <u>3 &amp; 3</u>  | <u>132</u> | <u>123</u>                       | <u>63</u>                     | <u>60</u>                     |

| <u>22</u>     | <u>16</u>           | <u>144</u>                    | <u>12</u>                | <u>3 &amp; 3</u>  | <u>132</u> | <u>120</u>                       | <u>63</u>                     | <u>57</u>                     |

| <u>23</u>     | <u>16</u>           | <u>144</u>                    | <u>24</u>                | <u>3 &amp; 3</u>  | <u>132</u> | <u>114</u>                       | <u>60</u>                     | <u>54</u>                     |

| <u>24</u>     | <u>16</u>           | <u>144</u>                    | <u>48</u>                | 3 & 3             | <u>132</u> | <u>102</u>                       | <u>54</u>                     | <u>48</u>                     |

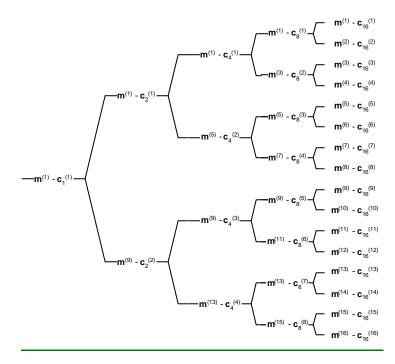

## 6.2.3 Training sequences for spread bursts

In this subclause, the training sequences for usage as midambles are defined. The training sequences, i.e. midambles, of different users active in the same cell and same time slot are cyclically shifted versions of one single basic midamble code. The applicable basic midamble codes are given in Annex C.1.

The basic midamble codes in Annex C.1 are listed in hexadecimal notation. The binary form of the basic midamble code shall be derived according to table [XX] below.

Table [XX]: Mapping of 4 binary elements  $m_i$  on a single hexadecimal digit

| $\frac{4 \text{ binary elements } m_i}{m_i}$ | Mapped on hexadecimal digit |

|----------------------------------------------|-----------------------------|

| <u>-1 -1 -1 -1</u>                           | 0                           |

| <u>-1 -1 -1 1</u>                            | 1                           |

| <u>-1 -1 1 -1</u>                            | 2                           |

| <u>-1 -1 1 1</u>                             | <u>3</u>                    |

| <u>-1 1-1-1</u>                              | 4                           |

| <u>-1 1-1 1</u>                              | <u>5</u>                    |

| <u>-1 1 1 -1</u>                             | <u>6</u>                    |

| <u>-1 1 1 1</u>                              | 7                           |

| <u>1-1-1-1</u>                               | <u>8</u>                    |

| <u>1-1-1 1</u>                               | 9                           |

| <u>1-1 1-1</u>                               | <u>A</u>                    |

| <u>1-1 1 1</u>                               | <u>B</u>                    |

| <u>1 1-1-1</u>                               | <u>C</u>                    |

| 1 1-1 1                                      | <u>D</u>                    |

| <u>1 1 1-1</u>                               | E                           |

| 1111                                         | <u>F</u>                    |

For each particular basic midamble code, its binary representation can be written as a vector  $\mathbf{m}_{p}$ :

$$\mathbf{m}_{P} ? ? m_{1}, m_{2}, ..., m_{P}?$$

(1)

According to Annex C.1, the size of this vector  $\underline{\mathbf{m}_{p}}$  is P=128. As QPSK modulation is used, the training sequences are transformed into a complex form, denoted as the complex vector  $\underline{\mathbf{m}_{p}}$ :

$$\underline{\mathbf{m}}_{P}$$

?  $\underline{m}_{1},\underline{m}_{2},...,\underline{m}_{P}$  ? (2)

The elements  $\underline{m}_i$  of  $\underline{\mathbf{m}}_{\mathrm{P}}$  are derived from elements  $\underline{m}_i$  of  $\underline{\mathbf{m}}_{\mathrm{P}}$  using equation (3):

$$\underline{m}_i$$

?  $(j)^i$ ? $m_i$  for all  $i$ ? 1,..., $P$  (3)

Hence, the elements  $\underline{m}_i$  of the complex basic midamble code are alternating real and imaginary.

To derive the required training sequences, this vector  $\underline{\mathbf{m}}_{P}$  is periodically extended to the size:

$$i_{\text{max}} ? L_m ? (K ? 1)W$$

(4)

Notes on equation (4):

K and W are taken from Annex C.1

So we obtain a new vector **m** containing the periodic basic midamble sequence:

$$\underline{\mathbf{m}} ? '\underline{\underline{m}}_{1}, \underline{\underline{m}}_{2}, ..., \underline{\underline{m}}_{i_{\max}} '? '\underline{\underline{m}}_{1}, \underline{\underline{m}}_{2}, ..., \underline{\underline{m}}_{L_{m}?(K?1)W} '\underline{\underline{l}}$$

(5)

The first P elements of this vector  $\underline{\mathbf{m}}$  are the same ones as in vector  $\underline{\mathbf{m}}_{\mathrm{P}}$ , the following elements repeat the beginning:

$$\underline{m}_i$$

?  $\underline{m}_{i?P}$  for the subset  $i$ ?  $(P?1),...,i_{\text{max}}$  (6)

<u>Using this periodic basic midamble sequence</u>  $\underline{\mathbf{m}}$  for each user k a midamble  $\underline{\mathbf{m}}^{(k)}$  of length  $L_m$  is derived, which can be written as a user specific vector:

$$\underline{\mathbf{m}}^{(k)} ? \underline{\mathcal{m}}_{1}^{(k)}, \underline{m}_{2}^{(k)}, \dots, \underline{m}_{L_{m}}^{(k)} \underline{\mathcal{m}}_{1}^{(k)} \underline{\mathcal{m}}_{$$

The  $L_m$  midamble elements  $\underline{m}_i^{(k)}$  are generated for each midamble of the k users (k = 1,...,K) based on:

$$\underline{m}_{i}^{(k)}$$

?  $\underline{m}_{i?(K?k)W}$  with  $i$  ? 1,..., $L_{m}$  and  $k$  ? 1,..., $K$  (8)

The midamble sequences derived according to equations (7) to (8) have complex values and are not subject to channelisation or scrambling process, i.e. the elements  $\underline{\underline{m}_{i}^{(k)}}$  represent complex chips for usage in the pulse shaping process at modulation.

The term 'a midamble code set' or 'a midamble code family' denotes K specific midamble codes  $\underline{\mathbf{m}}^{(k)}$ : k=1,...,K, based on a single basic midamble code  $\underline{\mathbf{m}}_{P}$  according to (1).

#### 6.2.3.1 Midamble Transmit Power

If in the downlink all users in one time slot have a common midamble, the transmit power of this common midamble is such that there is no power offset between the data part and the midamble part of the transmit signal within the time slot.

In the case of user specific midambles, the transmit power of the user specific midamble is such that there is no power offset between the data parts and the midamble part for this user within one slot.

## 6.2.4 Beamforming

Beamforming is same as that of the 3.84Mcps TDD, cf. [5.2.4 Beamforming].

## 6.3 Common physical channels

### 6.3.1 Primary common control physical channel (P-CCPCH)

The BCH as described in subclause 'Common Transport Channels' is mapped onto the Primary Common Control Physical Channels (P-CCPCH1 and P-CCPCH2). The position (time slot / code) of the P-CCPCHs is fixed in the 1.28Mcps TDD. The P-CCPCHs are mapped onto the first two code channels of timeslot#0 with spreading factor of 16, see subclause 'Common Transport Channels'. The P-CCPCH is always transmitted with an antenna pattern configuration that provides whole cell coverage.

#### 6.3.1.1 P-CCPCH Spreading

The P-CCPCH uses fixed spreading with a spreading factor SF = 16. The P-CCPCH1 and P-CCPCH2 always use channelisation code  $c_{Q?16}^{(k?1)}$  and  $c_{Q?16}^{(k?2)}$  respectively.

#### 6.3.1.2 P-CCPCH Burst TypesFormat

The burst format as described in section 6.2.2 is used for the P-CCPCH. No TFCI is applied for the P-CCPCH.

#### 6.3.1.3 P-CCPCH Training sequences

The training sequences, i.e. midambles, as described in the subclause on midamble generation are used for the P-CCPCH. The basic midamble code m<sup>(1)</sup> is used for P-CCPCHs as training sequence.

### 6.3.2 Secondary common control physical channel (S-CCPCH)

PCH and FACH are mapped onto one or more secondary common control physical channels (S-CCPCH). In this way the capacity of PCH and FACH can be adapted to the different requirements. The time slot and codes used for the S-CCPCH are broadcast on the BCH.

#### 6.3.2.1 S-CCPCH Spreading

The S-CCPCH uses fixed spreading with a spreading factor SF = 16. The S-CCPCHs (S-CCPCH 1 and S-CCPCH 2) are always used in pairs, mapped onto two code channels with spreading factor 16. There can be more than one pair of S-CCPCHs in use in one cell.

#### 6.3.2.2 S-CCPCH Burst Types Format

The burst format as described in section 6.2.2 is used for the S-CCPCH. TFCI may be applied for S-CCPCHs.

#### 6.3.2.3 S-CCPCH Training sequences

The training sequences, i.e. midambles, as described in the subclause on midamble generation, are also used for the S-CCPCH.

### 6.3.3 Fast Physical Access CHannel (FPACH)

The Fast Physical Access CHannel (FPACH) is used by the Node B to carry, in a single burst, the acknowledgement of a detected signature with timing and power level adjustment indication to a user equipment.

FPACH makes use of one resource unit only at spreading factor 16, so that its burst is composed by 44 symbols. The spreading code, training sequence and time slot position are configured by the network and signalled on the BCH.

#### 6.3.3.1 FPACH burst

The FPACH burst contains 32 information bits.

Table X reports the content description of the FPACH information bits and their priority order.

Table X: FPACH information bits description

| Information field                                               | <u>Length</u><br>(in bits) |

|-----------------------------------------------------------------|----------------------------|

| Signature Reference Number                                      | 3 (MSB)                    |

| Relative Sub-Frame Number                                       | <u>2</u>                   |

| Received starting position of the UpPCH (UpPCH <sub>POS</sub> ) | <u>11</u>                  |

| Transmit Power Level Command for RACH message                   | <u>Z</u>                   |

| Reserved bits                                                   | 9 (LSB)                    |

| (default value: 0)                                              |                            |

In the use and generation of the information fields is explained in TS25.224 sub-clause 5.6.2.1

#### 6.3.3.1.1 Signature Reference Number

The reported number corresponds to the numbering principle for the cell signatures as described in subclause 9.3.

The Signature Reference Number value range is 0 – 7 coded in 3 bits such that:

bit sequence(0 0 0) corresponds to the first signature of the cell; ...; bit sequence (1 1 1) corresponds to the 8<sup>th</sup> signature of the cell.

#### 6.3.3.1.2 Relative Sub-Frame Number

The Relative Sub-Frame Number value range is 0 – 3 coded such that:

bit sequence (0 0) indicates one sub-frame difference; ...; bit sequence (1 1) indicates 4 sub-frame difference.

#### 6.3.3.1.3 Received starting position of the UpPCH (UpPCH<sub>POS</sub>)

The received starting position of the UpPCH value range is 0 – 2047 coded such that:

bit sequence (0 0 ... 0 0 0) indicates the received starting position zero chip; ...; bit sequence (1 1 ... 1 1 1) indicates the received starting position 2047\*1/8 chip.

#### 6.3.3.1.4 Transmit Power Level Command for the RACH message

The transmit power level command is transmitted in 7 bits.

#### 6.3.3.2 FPACH Spreading

The FPACH uses only spreading factor SF=16 as described in subclause 6.2.1.1. The set of admissible spreading codes for use on the FPACH are broadcast on the BCH (within the FPACH configuration parameters on the BCH).

#### 6.3.3.2 FPACH Burst Format

The burst format as described in section 6.2.2 is used for the FPACH.

#### 6.3.3.3 FPACH Training sequences

The training sequences, i.e. midambles, of different users active in the same time slot are time shifted versions of a single periodic basic code. The basic midamble codes as described in the subclause about midamble generation are used for FPACH.

#### 6.3.3.4 FPACH timeslot formats

The FPACH uses slot format #0 of the DL time slot formats given in subclause 6.2.2.4.1.1.

## 6.3.43 The physical random access channel (PRACH)

The RACH is mapped onto one or more uplink physical random access channels (PRACH). In such a way the capacity of RACH can be flexibly scaled depending on the operators need.

#### 6.3.34.1 PRACH Spreading

The uplink PRACH uses either spreading factor SF=16 or SF=8 or SF=4 as described in subclause 6.2.1.4. The set of admissible spreading codes for use on the PRACH and the associated spreading factors are broadcast on the BCH (within the RACH configuration parameters on the BCH).

The uplink PRACH uses either spreading factor SF=16 or SF=8 as described in subclause of 'The Random Access Channel (RACH)'. The PRACH configuration (time slot number and assigned spreading codes) is broadcast through the BCH.

### 6.3.34.2 PRACH Burst TypesFormat

The burst format as described in section 6.2.2 is used for the PRACH.

#### 6.3.34.3 PRACH Training sequences

The training sequences, i.e. midambles, of different users active in the same time slot are time shifted versions of a single periodic basic code. The basic midamble codes as described in subclause about midamble generation are used for PRACH.

#### 6.3.34.4 PRACH timeslot formats

The PRACH uses the following time slot formats taken form the uplink timeslot formats described in sub-clause 6.2.2.4.1.2:

| <u>Spreading</u> | Slot Format |

|------------------|-------------|

| <u>Factor</u>    | <u>#</u>    |

| <u>16</u>        | 0           |

| 8                | <u>10</u>   |

| <u>4</u>         | <u>25</u>   |

#### 6.3.34.5 Association between Training Sequences and Channelisation Codes

The association between training sequences and channelisation codes of PRACH in the 1.28McpsTDD is same as that of the DPCH.

### 6.3.45 The synchronisation channels (DwPCH, UpPCH)

There are two dedicated physical synchronisation channels—DwPCH and UpPCH in each 5ms sub-frame of the 1.28Mcps TDD. DwPCH is used for the down link synchronisation and UpPCH is used for the up link synchronisation.

The position and the contents of the DwPCH are equal to the DwPTS as described in the subclause of the 'frame structure'. While the position and the contents of the UpPCH are equal to the UpPTS.

The DwPCH is transmitted at each sub-frame with an antenna pattern configuration which provides whole cell coverage. Furthermore it is transmitted with a constant power level which is signalled by higher layers.

The burst structure of the DwPCH (DwPTS) is described in the figure X1.

Figure X1: burst structure of the DwPCH ( DwPTS)

Note: 'GP' for 'Guard Period'

The burst structure of the UpPCH (UpPTS) is described in the figure X2.

Figure X2: burst structure of the UpPCH (UpPTS)

The SYNC DL code in DwPCH and the SYNC UL code in UpPCH are not spreaded. The details about the SYNC DL and SYNC UL code are described in the corresponding subclause and annex in TS25.223.

## 6.3.56 Physical Uplink Shared Channel (PUSCH)

For Physical Uplink Shared Channel (PUSCH) the burst structure of DPCH as described in subclause 6.2 shall be used. User specific physical layer parameters like power control, timing advance or directive antenna settings are derived from the associated channel (FACH or DCH). PUSCH provides the possibility for transmission of TFCI in uplink.

## 6.3.67 Physical Downlink Shared Channel (PDSCH)

For Physical Downlink Shared Channel (PDSCH) the burst structure of DPCH as described in subclause 6.2 shall be used. User specific physical layer parameters like power control or directive antenna settings are derived from the associated channel (FACH or DCH). PDSCH provides the possibility for transmission of TFCI in downlink.

To indicate to the UE that there is data to decode on the DSCH, three signalling methods are available:

- 1) using the TFCI field of the associated channel or PDSCH;

- 2) using on the DSCH user specific midamble derived from the set of midambles used for that cell:

- 3) using higher layer signalling.

When the midamble based method is used, the UE shall decode the PDSCH if the PDSCH was transmitted with the midamble assigned to the UE by UTRAN, see 6.6.1.1.2. For this method no other physical channels may use the same time slot as the PDSCH and only one UE may share the PDSCH time slot at the same time.

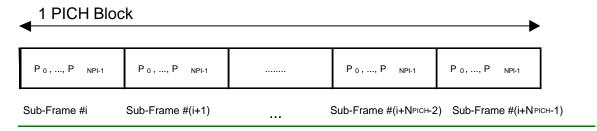

## 6.3.78 The Page Indicator Channel (PICH)

The Paging Indicator Channel (PICH) is a physical channel used to carry the Paging Indicators. The PICH is always transmitted at the same reference power level and with the same antenna pattern configuration as the P-CCPCH.

There are always two codes with SF=16 used for PICH. Figure [XX] depicts the PICH structure and the numbering order of the transported bits, N<sub>PIB</sub>, where N<sub>PIB</sub> is equal to 176 bits.

Figure: Transmission and numbering of paging indicators carrying bits on the PICH burst

In each PICH burst,  $N_{PL}$  paging indicators are transmitted, using  $L_{PL}=2$ ,  $L_{PL}=4$  or  $L_{PL}=8$  symbols.  $L_{PL}$  is called the paging indicator length. The number of paging indicators  $N_{PL}$  per PICH burst is given by the paging indicator length, which are both known by higher layer signalling. In table [XX] this number is shown for the different possibilities of burst types and paging indicator lengths.

Table [XX]: Number N<sub>Pl</sub> of paging indicators in a PICH burst for the different paging indicator lengths (L<sub>Pl</sub>)

|                           | <u>L<sub>PI</sub> = 2</u> | <u>L<sub>Pl</sub> = 4</u> | <u>L<sub>Pl</sub> = 8</u> |

|---------------------------|---------------------------|---------------------------|---------------------------|

| Number of PI per timeslot | <u>N<sub>PI</sub>=44</u>  | <u>N<sub>PI</sub>=22</u>  | <u>N<sub>PI</sub>=11</u>  |

As shown in figure [XX], the paging indicators of  $N_{PICH}$  consecutive sub-frames form a PICH block,  $N_{PICH}$  is configured by higher layers. Thus,  $N_{P}=N_{PICH}*N_{PL}$  paging indicators are transmitted in each PICH block.

Figure [XX]: Structure of a PICH block

The value PI (PI = 0, ...,  $N_P$ -1) calculated by higher layers for use for a certain UE, see [15], is associated to the paging indicator  $P_q$  in the  $n^{th}$  frame of one PICH block, where q is given by

$a = PI \mod N_{PI}$

$n = PI \operatorname{div} N_{PI}$ .

The PI bitmap in the PCH data frames over Iub contains indication values for all possible higher layer PI values, see [16]. Each bit in the bitmap indicates if the paging indicator  $P_q$  associated with that particular PI shall be set to 0 or 1. Hence, the calculation in the formulas above is to be performed in Node B to make the association between PI and  $P_q$ .

The coding of Paging Indicator for 1.28Mcps TDD is same as that for 3.84Mcps TDD, cf.[5.3.7 'The Paging Indicator Channel (PICH)'].

## 6.4 Transmit Diversity for DL Physical Channels

Table X1 summarizes the different transmit diversity schemes for different downlink physical channel types in 1.28Mcps TDD that are described in [9].

<u>Table X1: Application of Tx diversity schemes on downlink physical channel types in 1.28Mcps TDD</u>

<u>"X" – can be applied, "–" – must not be applied</u>

| Physical channel type | Open loop   | TxDiversity | Closed loop TxDiversity |

|-----------------------|-------------|-------------|-------------------------|

|                       | <u>TSTD</u> | Block STTD  |                         |

| P-CCPCH               | =           | <u>¥</u>    | =                       |

| <del>DwPCH</del>      | X           | =           | =                       |

| <u>FPACH</u>          | =           | :           | <u></u> <u></u> ×       |

| <del>DPCH</del>       | =           | =           | <u>X</u>                |

| Physical channel type | Open loop   | <u>TxDiversity</u> | Closed loop TxDiversity |

|-----------------------|-------------|--------------------|-------------------------|

|                       | <u>TSTD</u> | Block STTD         |                         |