# TSGR1#18(01)0142

TSG-RAN Working Group 1 meeting #18 Boston, USA January 15-18, 2001

**Agenda item:** Release 4

Source: Samsung and Nokia

**Title:** Answers to Comments on TR 25.840 "Terminal Power Saving Features"

**Document for:** Discussion and approval

\_\_\_\_\_

## Introduction

In this contribution, we present answers to the comments on the TR 25.840 Terminal Power Saving features v2.0.0 [1] made in [2,3,4].

# Gated DPCCH transmission scheme in FDD – Terminology

As commented in [2], "gated DPCCH transmission", "gating", or "gating mode" are used interchangeably in current TR 25.840. This may cause some misunderstanding or confusion. To solve this problem, a common term, e.g., "gating" can be used. However, "normal gating period" and "embedded DPDCH period" clearly have different meanings. "Normal gating period" means the period during which DPDCH transmission does not occur either in downlink or uplink. On the other hand, "embedded DPDCH period" means that the period during which data with restricted TFS is transmitted on DPDCH. In spite of the difference in the meaning, "normal gating period" and "embedded DPDCH period" also may cause some misunderstanding or confusion. To solve this problem, "non-DPDCH period" can be used instead of "normal gating period".

# Detection of DPDCH frame during gating

"RX gating DRX cycle" is defined to indicate when downlink data transmission can occur during gating. Thus, UE knows when UE can detect sensible TFCI word transmitted over a whole frame, and UE determines the existence of downlink DPDCH frame by decoding downlink TFCI in the frames defined by RX gating DRX cycle. However, uplink DPDCH transmission can occur in any frames. Thus, Node B does not know when uplink DPDCH transmission can occur. Furthermore, if Node B tries to decode TFCI when uplink DPDCH transmission does not exist, then an errorneous operation may occur. To avoid the errorneous operation caused by incomplete TFCI word, the TR provides a possible solution that Node B performs pilot energy comparison to detect uplink DPDCH transmission by taking into account that when uplink DPDCH transmission occurs during gating, pilot bits are transmitted in every slot. If pilot energy comparison indicates that pilot bits (or equivalently, TFCI bits) are transmitted over the whole frame, then TFCI decoding is performed. Finally, it is noted that meaningless TFCI is transmitted from UE during non-DPDCH period to ease UE operation by turning on/off the UE Tx side slotwise.

# Power control parameters

Among the power control parameters, both DPC\_MODE 1 and power control Algorithm 2 cannot be used. The TR provides possible solutions in section 6.1.7.1. In summary, the solutions are as follows:

- During gating, DPC\_MODE 0 is used instead of DPC\_MODE 1 without explicit signaling.

- During gating, Algorithm 1 is used instead of Algorithm 2 without explicit signaling.

Recovery period and different power control step were introduced to compensate the effect of reduced power control rate during gating. Specification of recovery period and power control step needs further discussion. The outer loop power control (OL PC) based on CRC proposed by Nokia [6,7] also will be considered in specifying recovery period and power control step.

## Operation with other features

#### STTD

Since STTD encoding is performed for each time slot unit, there does not exist the case that four consecutive bits overlap a slot border. Thus, there is no impact by gating. For the convenience, we summarize STTD encoding of DL DPCH described in [5] as follows:

- The diversity antenna pilot bit pattern is obtained by STTD encoding only the pilot bits except the case that N<sub>pilot</sub>=2.

- For  $N_{pilot} = 2$ , the diversity antenna pilot pattern is obtained by STTD encoding the two pilot bits with the last two bits (data or DTX) of the second data field (data2) of the slot.

- STTD encoding for the DPDCH, TPC, and TFCI fields is done as described in subclause 5.3.1.1.1 of [5]. The STTD encoding operation described above clearly reveals that there is no impact by gating.

### Compressed mode

We agree that there are impacts of compressed mode on the practically achievable gains from gating. However, some realistic values have to be used for the percentage of compressed mode over UE tum-on time due to the fact that compressed mode deteriorates the capacity according to TSGR4#14(00)0960. The impact of compressed mode on practically achievable gains from gating is treated in section about performance.

#### SSDT

Regarding SSDT, there are two solutions. The first solution is that gating shall be disabled when SSDT is initiated with SSDT as described in the current TR. The termination of gating and the initiation of SSDT can be performed by a single higher layer signaling message. Thus, no additional signalling is required.

The second solution that we propose in this paper is to modify the operation of SSDT so that gating can be used even if SSDT is activated. The proposed modification can be summarized as follows:

- If the condition for initiating gating is satisfied when SSDT is activated or SSDT is activated during gating, both UE and Node B perform normal soft handover operation without explicit signaling. In detail, UE generates uplink TPC command after radio link combination and Node B acts as if it is the primary cell.

- If SSDT is still activated after gating is terminated, the normal SSDT operation is resumed without explicit signaling. Finally, we note that initiation and termination of gating is independent of initiation and termination of SSDT.

# Impact to WGs

### WG1

Obviously, some changes will be needed to the text of TS 25.212 and TS 25.214. However, since gating does not make any change in physical channels, the text of TS 25.211 does not need to be changed. Also, there is no need to modify the definition of measurements of TS 25.215.

#### WG3

In Tdoc R1-01-0032 "Revision of TR25.840 Terminal Power Saving Features", according to the decision from RAN WG1 meeting #17 on description of impacts to RAN WG3, RAN WG3 TR 25.938 "Terminal Power Saving Features (Iur/Iub aspects)" is referenced. We note that TR 25.938 treats the impact on WG3 specifications.

#### WG4

- Tx power = 10 dBm

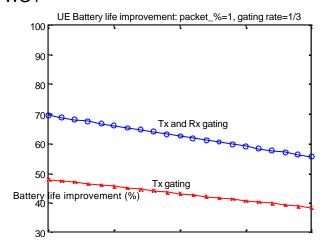

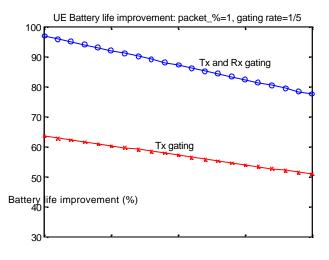

The two figures show that battery life improvement is sufficiently large enough to use gating even if the percentage of compressed mode duration over UE turn-on duration is 20 %.

### UE battery life enhancements

Of course, the relative power consumption of different paths will have effect on achieved battery saving figures. Naturally, if receiver consumes e.g. 10 A or 100 mA has major effect to calculated battery saving results. This is also valid in the TX side. All in all, the main players here are main amplifier and it's efficiency in addition to maximum TX power i.e. 125 mW. Of course, there will be some differencies in the used Duplex filters and switchs which might result bit different results depending on the implementation.

# Reference and history sections

In the revised TR, the overlapping references will be solved and the history section will be correctly modified.

## Conclusion

In this paper, we present clarification of the technical report and also propose a new solution for interaction of gating with SSDT. We propose to reflect the agreed part of this paper into revision of the technical report.

### **Contact Points**

Juho Lee <u>juholee@samsung.com</u>

Sungoh Hwang <u>sungoh@samsung.com</u>

Markku Tarkiainen <u>markku.tarkiainen@nokia.com</u>

### References

- [1] 3G TR 25.840 (v2.0.0), "Terminal power saving features".

- [2] R1-01-0038, "Comments on TR 25.840 Terminal Power Saving features", Ericsson.

- [3] R1-01-0039, "Impact of compressed mode on the performance of DPCCH gating", Ericsson.

- [4] R1-01-0114, "Interactions between DPCCH gating and monitoring for handover purposes", Nortel Networks.

- [5] 3GPP TS 25.211: "Physical channels and mapping of transport channels onto physical channels (FDD)".

- [6] R1-01-0011, "Revision of TR25.840 Terminal Power Saving Features including changes to facilitate OL PC to be based on CRC during DPCCH gating", Nokia

- [7] R1-01-0009, "Further clarifications on outer loop power control during DPCCH gating", Nokia