# TSGR1#18(01)0008

TSG-RAN Working Group 1 meeting #18 Boston, USA January 15<sup>th</sup> – 18<sup>th</sup>, 2001

Agenda item: Adhoc 24

Source: Nokia

**Title:** Relationship between frame error rate and TrCH block error rate

**Document for:** Discussion

#### 1. Introduction

This paper contains simulation results on the relationship between frame error rate and TrCH block error rate. It has been claimed earlier that all the blocks , which are encoded together with turbo coding are in error at the same time. However, it is possible , according to release99 specs, that there are several turbo encoding blocks in each TTI. In this short study, it was simulated, how the relationship between block errors and frame errors vary , depending on whether there is only one or several encoding blocks per TTI.

### 2. Simulation parameters

Table 1 shows the simulation parameters, see the annex. The simulations were conducted for an input source rate of 800 kbs and rate 1/2 turbo codes were used. The simulations were conducted by using two multicodes both of spreading factor 8. For all the simulations Pedestrian A Channel with mobile speed of 5 km/h was used. The spreading factor of all the 20 interfering users was chosen as 256. The frame length , also interleaving period, was 10 ms. The simulation were done for a Target Frame Error Rate of 40 %. The simulations were done for single code block in a frame and also for multiple code blocks in a frame

#### 3. Simulation results

The relationship between block error rate and frame error rate was evaluated using the conditional probability  $P_j$ , which represents the probability that  $\dot{j}$  Transport Blocks (of a frame) is in error given that the frame is in error. The FERBLER relationship was also obtained using the following equation.

Comparison Ratio(CR) = (Transport Blocks in Error)/ (FramesInError \* NoOfTransportBlockInFrames)

The section 3.1 shows the simulation results for single code block in a frame and section 3.2 shows the simulation results for multiple code blocks in a frame.

#### 3.1 Single Code Block in a Frame

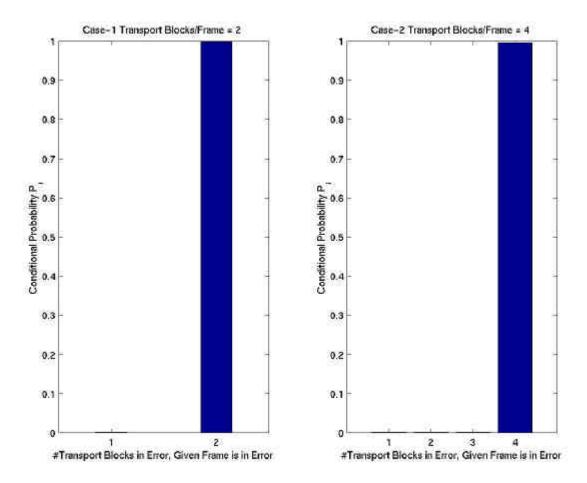

The simulations were done for two different cases, Case 1) the frame contains two transport blocks of length 4000 bits each and Case 2) the frame contains four transport blocks of length 2000 bits each. The simulation results are shown in Figure 3.1.1 and Table 3.1.1

Figure 3.1.1 Conditional Probabilities

| Case | Explanation                   | Comparison ratio (CR) |

|------|-------------------------------|-----------------------|

| 1    | ?? 2 TrCh blocks of 4000 bits | 0.999503              |

|      | ?? 1 code block of 8000 bits  |                       |

| 2    | ?? 4 TrCh blocks of 4000 bits | 0.997968              |

|      | ?? 1 code blocks of 4000 bits |                       |

**Table 3.1.1 Comparison Ratios**

## 3.2 Multiple Code Blocks in a Frame

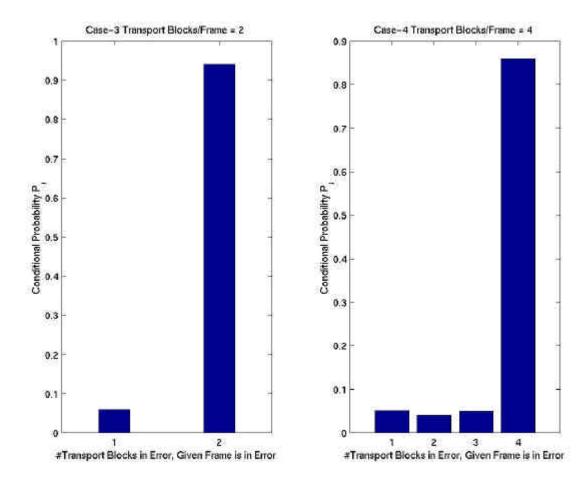

The simulations were done for two different cases, Case 3) the frame contains two transport blocks and two code blocks of length 4000 bits each and Case 4) the frame contains four transport blocks and four code blocks of length 2000 bits each. The simulation results are shown in Figure 3.2.1 and Table 3.2.1

Figure 3.2.1 Conditional Probabilities

| Case | Explanation                   | Comparison ratio (CR) |

|------|-------------------------------|-----------------------|

| 1    | ?? 2 TrCh blocks of 2000 bits | 0.970602              |

|      | ?? 2 code block of 8000 bits  |                       |

| 2    | ?? 4 TrCh blocks of 2000 bits | 0.929499              |

|      | ?? 4 code blocks of 2000 bits |                       |

**Table 3.2.1 Comparison Ratios**

## 4. Conclusions

It was shown with simulations that there is a high correlation between frame error rate and TrCH block error rate, even in the case when there are several code blocks per frame. It can be seen that there is very small difference between cases where there is only one or several coding blocks per frame. The results show that in both cases the TrCH block error rate is almost equal to the frame error rate. This means that usually all the transport blocks per frame are in error at the same time.

This means that it seems sensible to do the FHARQ ack/nacks and retransmissions at the frame level (TTI level), and not separately for each TrCH block.

**Annex 1: Table 1. Simulation assumptions**

| Parameter                        | Explanation/Assumption                                                                                               |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Chip Rate                        | 3.84 Mcps                                                                                                            |

| Closed loop Power Control        | ON                                                                                                                   |

| Channel Estimation               | CPICH                                                                                                                |

| PC error rate                    | 4%                                                                                                                   |

| PC delay                         | 1 slot                                                                                                               |

| Number of samples per chip       | 1                                                                                                                    |

| Propagation Conditions           | Pedestrian A 5 km/h                                                                                                  |

| Number of bits in AD converter   | Floating point simulations                                                                                           |

| Number of Rake Fingers           | Equals to number of taps in propagation condition models                                                             |

| Downlink Physical Channels and   | CPICH_Ec/lor = -10 dB                                                                                                |

| Power Levels                     | No PCCPCH                                                                                                            |

|                                  | No SCH                                                                                                               |

|                                  | OCNS_Ec/lor = power needed to get total power spectral density (lor) to 1, divided equally between interfering users |

|                                  | DPCH_Ec/lor = total power needed to meet the required BLER target                                                    |

| Number of interfering users      | 20 with SF 256                                                                                                       |

| Bit rates                        | 800 KBS                                                                                                              |

| TFCI model                       | Random symbols, ignored in a receiver but it is assumed that receiver gets error free reception of TFCI information. |

| Used OVSF and scrambling codes   | Codes are chosen from the allowed set                                                                                |

| $\hat{I}_{or}/I_{oc}$ values (G) | 6 dB                                                                                                                 |

| D (delay between transmissions)  | 6 TTls                                                                                                               |

| Other L1 parameters              | As Specified in latest L1 specifications                                                                             |