R1-00-0841

# 3G TR 25.928 V1.0.0 (2000-06)

Technical Report

3<sup>rd</sup> Generation Partnership Project (3GPP); Technical Specification Group (TSG); Radio Access Network (RAN); 1.28Mcps functionality for UTRA TDD Physical Layer

Reference DTS/TSGR-0125223 (25223-300.PDF)

> Keywords <keyword[, keyword]>

> > 3GPP

Postal address

Office address

Internet

secretariat@3gpp.org Individual copies of this deliverable can be downloaded from http://www.3gpp.org

**Copyright Notification**

No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

© 1999, 3GPP Organizational Partners (ARIB, CWTS, ETSI, T1, TTA, TTC). All rights reserved.

## Contents

| Forew   | ord                                                                        | . 7 |

|---------|----------------------------------------------------------------------------|-----|

| 1       | Scope                                                                      | . 8 |

| 2       | References                                                                 | . 8 |

| 3       | Abbreviations                                                              | . 8 |

| 4       | Radio Requirements                                                         | . 9 |

| 4.1     | Radio environments                                                         |     |

| 4.2     | Services                                                                   |     |

| 4.3     | Operational requirements                                                   |     |

| 4.3.1   | Deployment scenarios                                                       |     |

| 4.4     | Handover and Cell selection/reselection                                    |     |

| 4.5     | Particular characteristics of the low chip rate TDD                        | 11  |

| 5       | High level characteristics                                                 | 12  |

| 6       | Physical layer - General description                                       | 14  |

| 6.1     | General description of Layer 1                                             | 14  |

| 6.1.2   | Service provided to higher layers                                          | 14  |

| 6.2     | Document structure of the physical layer specification                     | 14  |

| 6.2.1   | Multiple Access                                                            |     |

| 6.2.2   | Channel coding and interleaving                                            |     |

| 6.2.3   | Modulation and spreading                                                   |     |

| 6.2.4   | Physical layer procedures                                                  |     |

| 6.2.5   | Physical layer measurements                                                | 15  |

| 7       | Physical channels and mapping of transport channels onto physical channels | 16  |

| 7.1     | Transport channels                                                         |     |

| 7.1.1   | Transport channels                                                         |     |

| 7.2     | Physical channels                                                          |     |

| 7.2.1   | Frame structure                                                            |     |

| 7.2.2   | Dedicated physical channel (DPCH)                                          | 17  |

| 7.2.2.1 |                                                                            |     |

| 7.2.2.2 | Burst Types                                                                | 17  |

| 7.2.2.2 | 2.1 Transmission of TFCI                                                   | 18  |

| 7.2.2.2 | 2.2 Transmission of TPC                                                    | 19  |

| 7.2.2.2 | 2.3 Timeslot formats                                                       | 21  |

| 7.2.2.2 | 2.3 Transmission of SS                                                     | 31  |

| 7.2.2.3 |                                                                            |     |

| 7.2.2.4 |                                                                            |     |

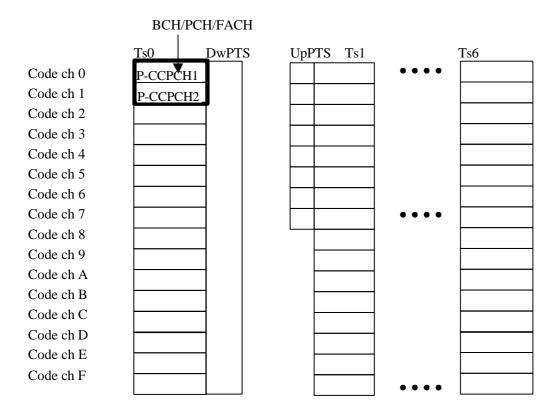

| 7.2.3   | Primary common control physical channel (P-CCPCH)                          |     |

| 7.2.3.1 |                                                                            |     |

| 7.2.3.1 | 1 6                                                                        |     |

| 7.2.3.1 | 51                                                                         |     |

| 7.2.3.1 |                                                                            |     |

| 7.2.3.2 |                                                                            |     |

| 7.2.3.2 | I E                                                                        |     |

| 7.2.3.2 |                                                                            |     |

| 7.2.3.2 |                                                                            |     |

| 7.2.3.3 |                                                                            |     |

| 7.2.3.3 |                                                                            |     |

| 7.2.3.3 | 71                                                                         |     |

| 7.2.3.3 |                                                                            |     |

| 7.2.3.3 |                                                                            |     |

| 7.2.3.4 |                                                                            |     |

| 1.4.5.5 | i nystear Opinik Snared Channel († 05011)                                  | +4  |

| 7.2.3.6        | Physical Downlink Shared Channel (PDSCH)                                                     | 42   |

|----------------|----------------------------------------------------------------------------------------------|------|

| 7.2.3.7        | The Page Indicator Channel (PICH)                                                            | 42   |

| 7.2.4          | Beacon function of physical channels                                                         | 44   |

| 7.2.4.1        | Location of physical channels with beacon function                                           | 44   |

| 7.2.4.2        | Physical characteristics of the beacon function                                              | 44   |

| 7.2.5          | Midamble Allocation for Physical Channels                                                    | 44   |

| 7.3            | Mapping of transport channels to physical channels                                           | 45   |

| 7.3.1          | Dedicated Transport Channels                                                                 | 45   |

| 7.3.2          | Common Transport Channels                                                                    | 46   |

| 7.3.2.1        | The Broadcast Channel (BCH)                                                                  | 47   |

| 7.3.2.2        | The Paging Channel (PCH)                                                                     |      |

| 7.3.2.2        | The Forward Channel (FACH)                                                                   |      |

| 7.3.2.3        | The Random Access Channel (RACH)                                                             |      |

| 7.3.2.4        | The Uplink Shared Channel (USCH)                                                             | 49   |

| 7.3.2.5        | The Downlink Shared Channel (DSCH)                                                           | 49   |

| Annex A        | A (Normative): Basic Midamble Codes                                                          |      |

| A.1            | Basic Midamble Codes for Burst Type 1 and PRACH Burst Type                                   |      |

| A.2            | Basic Midamble Codes for Burst Type 2                                                        |      |

| Annex E        | 3 (Informative): CCPCH Multiframe Structure                                                  | 54   |

| 8 N            | Iultiplexing and channel coding                                                              | 55   |

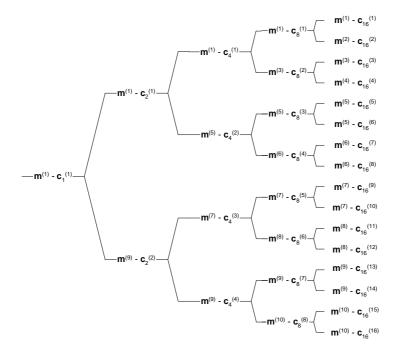

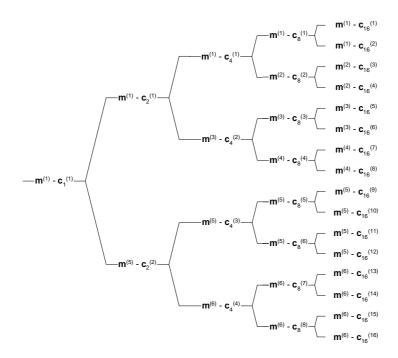

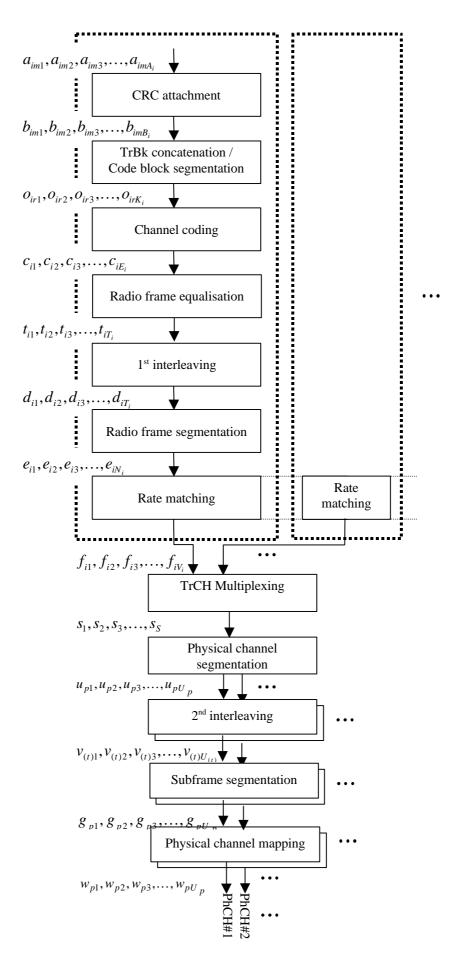

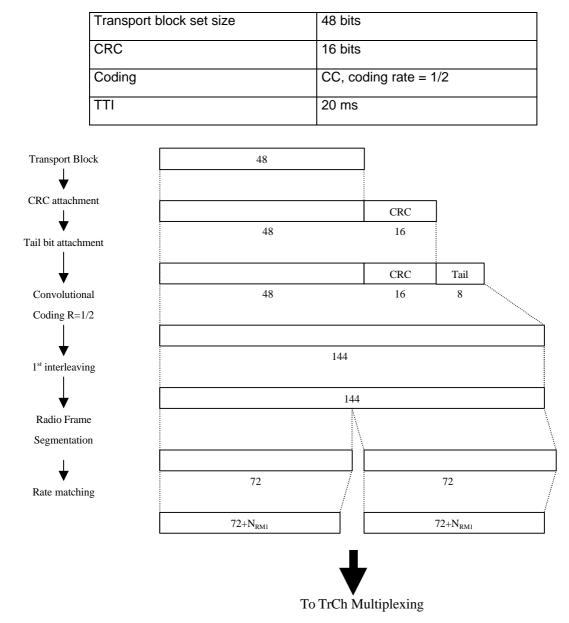

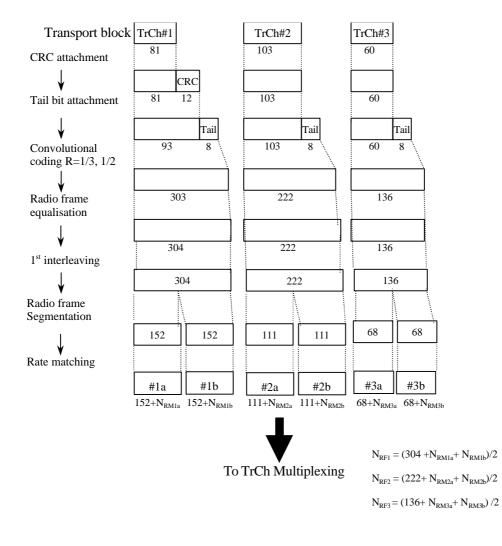

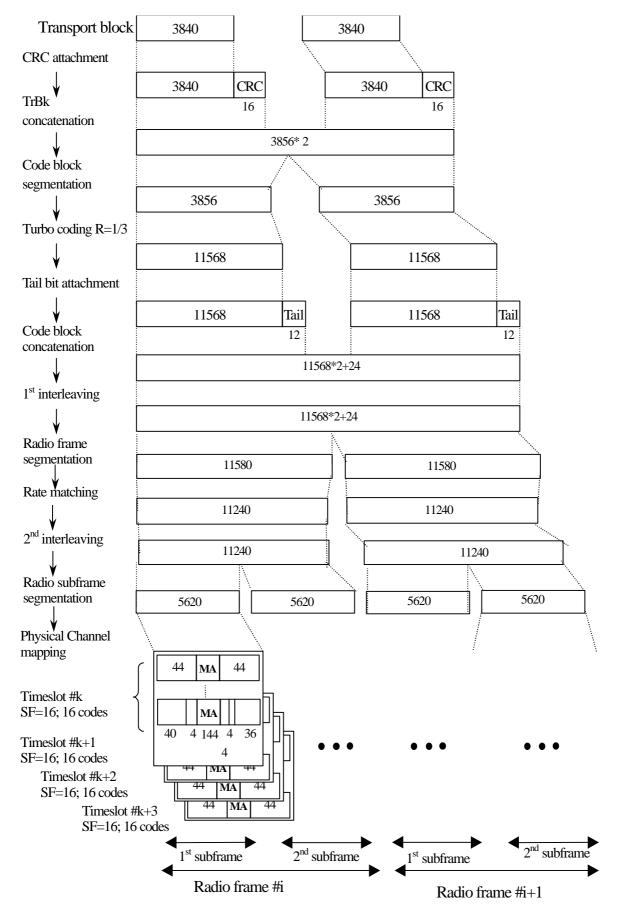

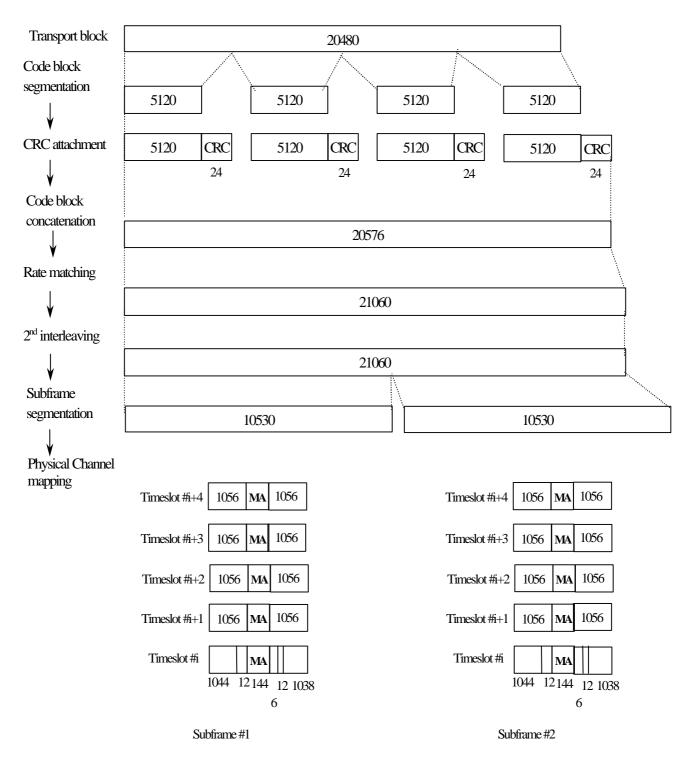

| 8.1            | Transport channel coding/multiplexing                                                        |      |

| 8.1.1          |                                                                                              |      |

| 8.1.1<br>8.1.2 | Error detection<br>Transport block concatenation and code block segmentation                 |      |

| 8.1.2<br>8.1.3 | Channel coding                                                                               |      |

| 8.1.5<br>8.1.4 | Radio frame size equalisation                                                                |      |

| 8.1.4<br>8.1.5 | 1st interleaving                                                                             |      |

| 8.1.6          | Radio frame segmentation                                                                     |      |

| 8.1.7          | Sub-frame segmentation                                                                       |      |

| 8.1.8          | Rate matching                                                                                |      |

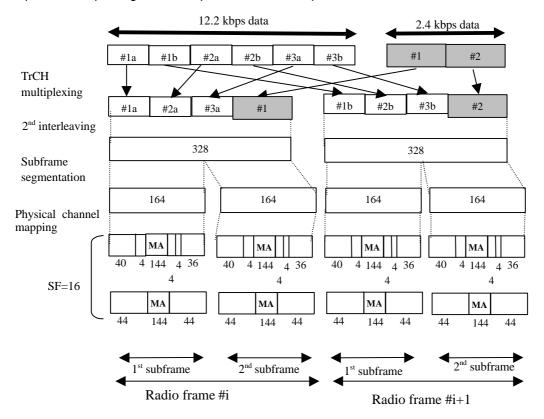

| 8.1.9          | TrCH multiplexing                                                                            |      |

| 8.1.10         | Physical channel segmentation                                                                |      |

| 8.1.10         | 2nd interleaving                                                                             |      |

| 8.1.11.1       | Frame related 2nd interleaving                                                               |      |

| 8.1.11.2       | , – –                                                                                        |      |

| 8.1.12         | Physical channel mapping                                                                     |      |

| 8.1.12         | Multiplexing of different transport channels onto one CCTrCH, and mapping of one CCTrCH onto |      |

| 0.1.15         | physical channels                                                                            | 60   |

| 8.1.13.1       | Allowed CCTrCH combinations for one UE                                                       |      |

| 8.1.13.1       |                                                                                              |      |

| 8.1.13.1       | -                                                                                            |      |

| 8.1.14         | Transport format detection                                                                   |      |

| 8.2            | Coding for layer 1 control                                                                   |      |

| 8.2.1          | Coding of transport format combination indicator (TFCI)                                      |      |

| 8.2.2          | Coding of Synchronisation Shift                                                              |      |

| 8.2.3          | Coding of Transmit Power Control (TPC)                                                       |      |

| 8.2.4          | Coding of the Paging Indicator                                                               |      |

|                |                                                                                              |      |

| 9 S            | preading and Modulation                                                                      | . 63 |

| 9.1            | Data modulation                                                                              | 63   |

| 9.1.2          | Mapping of bits onto signal point constellation                                              |      |

| 9.1.2.1        | QPSK modulation                                                                              |      |

| 9.1.2.2        | 8PSK modulation                                                                              |      |

| 9.1.3          | Symbol rate                                                                                  |      |

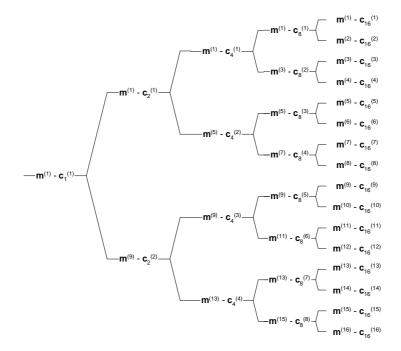

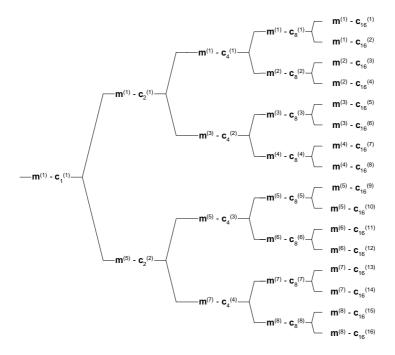

| 9.2            | Spreading modulation                                                                         |      |

| 9.2.1          | Basic spreading parameters                                                                   |      |

| 9.2.2          | Spreading codes                                                                              |      |

| 9.2.3          | Scrambling codes                                                                             |      |

| 9.2.4          | Spread and scrambled signal of data symbols and data blocks                                  |      |

| 9.3            | Synchronisation codes                                                                        | 64   |

| 10      | Physical layer procedures                        | 76 |

|---------|--------------------------------------------------|----|

| 10.1    | Transmitter Power Control                        | 76 |

| 10.1.2  | Uplink Control                                   | 76 |

| 10.1.2. | 2 Common Physical Channel                        | 77 |

| 10.1.3  | Downlink Control                                 |    |

| 10.1.3. | 1 Common Physical Channel                        | 77 |

| 10.1.3. |                                                  |    |

| 10.2    | Timing Advance                                   |    |

| 10.2.1  | With UL Synchronization                          |    |

| 10.2.1. | 1 The establishment of uplink synchronization    | 78 |

| 10.2.1. |                                                  |    |

| 10.2.1. |                                                  |    |

| 10.2.1. |                                                  |    |

| 10.3    | Synchronisation and Cell Search Procedures       |    |

| 10.3.1  | Cell Search                                      |    |

| 10.4    | Discontinuous transmission (DTX) of Radio Frames |    |

| 10.5    | Downlink Transmit Diversity                      |    |

| 10.5.1  | Transmit Diversity for DPCH                      |    |

| 10.5.2  | Transmit Diversity for SCH                       |    |

| 10.5.3  | Transmit Diversity for P-CCPCH                   |    |

| 10.5.4  | Transmit diversity for FPACH                     |    |

| 10.6    | Random Access Procedure                          |    |

| 10.6.1  | Preparation of random access                     |    |

| 10.6.2  | Random access procedures                         |    |

| 10.6.3  | Random access collision                          |    |

|         |                                                  |    |

|         | Physical layer measurements                      |    |

| 11.1    | Control of UE/UTRAN measurements                 |    |

| 11.1.1  | General measurement concept                      |    |

| 11.1.2  | Measurements for cell selection/reselection      |    |

| 11.1.3  | Measurements for Handover                        |    |

| 11.1.4  | Measurements for DCA                             |    |

| 11.1.5  | Measurements for timing advance                  |    |

| 11.2    | Measurement abilities for UTRA TDD               |    |

| 11.2.1  | UE measurement abilities                         |    |

| 11.2.1. |                                                  |    |

| 11.2.1. |                                                  |    |

| 11.2.1. |                                                  |    |

| 11.2.1. |                                                  |    |

| 11.2.1. |                                                  |    |

| 11.2.1. |                                                  |    |

| 11.2.1. |                                                  |    |

| 11.2.1. |                                                  |    |

| 11.2.1. |                                                  |    |

| 11.2.1. | · · · · ·                                        |    |

| 11.2.1. |                                                  |    |

| 11.2.1. |                                                  |    |

| 11.2.1. |                                                  |    |

| 11.2.2  | UTRAN measurement abilities                      |    |

| 11.2.2. |                                                  |    |

| 11.2.2. |                                                  |    |

| 11.2.2. |                                                  |    |

| 11.2.2. |                                                  |    |

| 11.2.2. |                                                  |    |

| 11.2.2. | 1                                                |    |

| 11.2.2. | · · · · · · · · · · · · · · · · · · ·            |    |

| 11.2.2. | 1                                                |    |

| 11.2.2. | 9 RX Timing Deviation                            | 85 |

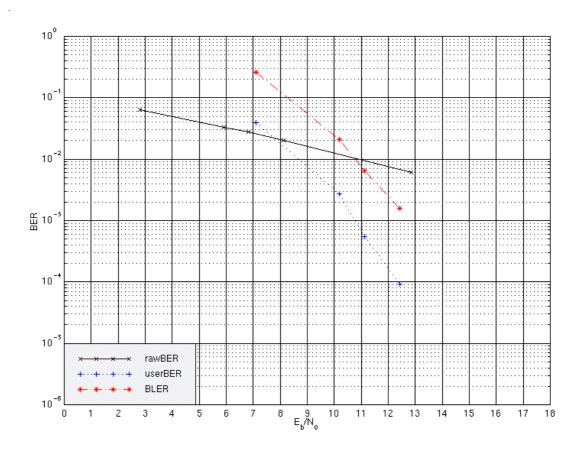

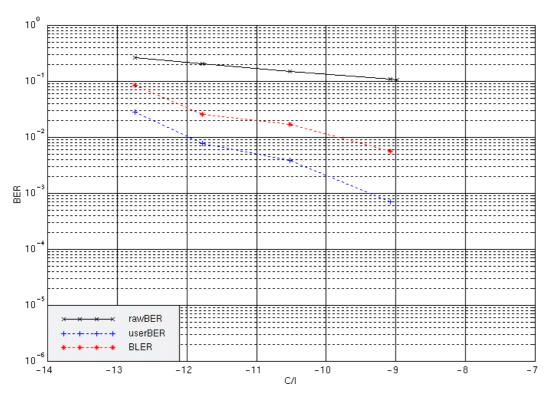

| 12 | Performance analysis of the low chip rate | 85 |

|----|-------------------------------------------|----|

| 13 | Examples of service mapping               | 93 |

| 14 | History1                                  | 03 |

### Foreword

This Technical Report has been produced by the 3GPP.

The contents of the present document are subject to continuing work within the TSG and may change following formal TSG approval. Should the TSG modify the contents of this TS, it will be re-released by the TSG with an identifying change of release date and an increase in version number as follows:

Version 3.y.z

where:

- x the first digit:

- 1 presented to TSG for information;

- 2 presented to TSG for approval;

- 3 Indicates TSG approved document under change control.

- y the second digit is incremented for all changes of substance, i.e. technical enhancements, corrections, updates, etc.

- z the third digit is incremented when editorial only changes have been incorporated in the specification.

### 1 Scope

This Technical Report describes the 1.28Mcps functionality for UTRA TDD physical layer, identifies commonalties and explains the differences to the 3.84Mcps chip rate. Suggestions for alignment will be provided too.

### 2 References

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- References are either specific (identified by date of publication, edition number, version number, etc.) or non-specific.

- For a specific reference, subsequent revisions do not apply.

- For a non-specific reference, the latest version applies.

- [1] TS 25.201: "Physical Layer General Description"

- [2] TS 25.221: "Physical channels and mapping of transport channels onto physical channels (TDD)"

- [3] TS 25.222: "Multiplexing and channel coding (TDD)"

- [4] TS 25.223: "Spreading and modulation (TDD)"

- [5] TS 25.224: "Physical layer procedures (TDD)"

- [6] TS 25.225: "Physical layer Measurements (TDD)"

### 3 Abbreviations

For the purposes of the present document, the following abbreviations apply:

| CDMA | Code Division Multiple Access |

|------|-------------------------------|

| PN   | Pseudo Noise                  |

| QPSK | Quadrature Phase Shift Keying |

| RACH | Random Access Channel         |

### 4 Radio Requirements

### 4.1 Radio environments

The radio environment recommended by ITU like indoor environment, pedestrian environment, vehicular environment (120km/h) should be well supported by the low chip rate TDD option.

### 4.2 Services

As one option of TDD mode, the low chip rate option should provide the basic service (bearer service). For a IMT-2000 compliant system corresponding to ITU requirement, for the indoor environment, up to 2Mbps data service should be provided. And for outdoor pedestrian environment, the data service should be up to 384kbps and more. For the UE in moving environment (vehicular speed less than 120km/h), the data rate supported should be 384 and more kbps.

### 4.3 Operational requirements

The low chip rate TDD option should provide the flexibility to be used for high spot or high density area to provide high speed data service or to provide enhanced coverage or be used alone as macro cell to provide the service coverage. It should allow deployment together with FDD system, with high chip rate TDD system, and be similar as high chip rate TDD deploying with GSM.

### 4.3.1 Deployment scenarios

For the low chip rate TDD option, the deployment should be flexible for all the scenarios like macro cell, micro cell and pico cell, etc. and also should provide the fixed wireless access.

### [Description:]

For the low chip rate TDD option, the deployment should be flexible for all the scenarios like macro cell, micro cell and pico cell, etc. and also should provide the fixed wireless access.

Dependent on the kind of interference accepted by the operator, the operator can vary the max. cell radius in a trade-off with UL - DL interference with the following limitations:

| Case                                                                   | Max. cell radius |

|------------------------------------------------------------------------|------------------|

| no UpPTS – DwPTS interference allowed                                  | 11.25 km         |

| UpPTS – DwPTS interference allowed, but no interference to TS0 allowed | 22.5 km          |

| no TS1 – DwPTS interference allowed, other interference allowed        | 30 km            |

| TS1 – DwPTS interference allowed, but no interference to TS0 allowed   | 41.25 km         |

| Table: | Interference | scenarios | and the | correspondir | ng max. | cell radius |

|--------|--------------|-----------|---------|--------------|---------|-------------|

|        |              |           |         |              |         |             |

#### [Rational:]

The guard period of 75 s between the DwPTS and the UpPTS is designed to avoid interference between the UpPTS (UL) and the DwPTS (DL). Therefore the cell size ensuring the interference free reception of the DwPTS is guaranteed to a size of approximately 10 km in radius (exact value 11.25 km, assuming no delay spread).

Consequently, for bigger cell radii there is a conflict that the advanced UpPTS interfering the DwPTS reception of another UE being close by.

Even though the UpPTS – DwPTS interference is possible for bigger cell radii then 11.25 km, the impact on the quality of service can be low and acceptable for an operator willing to operate bigger cells.

There are three reasons for that:

The probability that the a UE is close to another UE is low - especially for big cells

The DwPTS needs not to be received by every mobile in every frame. A few DwPTSs being not received during initial cell search mean no big degradation.

The UpPTS is not transmitted every frame it is only needed for random access or handover. So the probability of disturbance is rather low.

It is recommended that the operator avoids interference of TS1 to TS0 by means of the choice of the cell radius. This interference would mean permanent interference for TS0.

The operators can judge the trade-off between quality of service and range and select the range accordingly.

The maximum cell radius  $d_{max}$  is dependent on the time  $t_{gap}$  between the potentially interfering UL signal and the potentially interfered DL signal by to following equation:

$$d_{\text{max}} = \frac{c t_{gap}}{2}$$

; c is velocity of light.

The following table shows the possible trade-offs between cell radius and interference:

| Potentially interfering<br>UL signal | Potentially interfered<br>DL signal | t <sub>gap</sub> in s | d <sub>max</sub> in km |

|--------------------------------------|-------------------------------------|-----------------------|------------------------|

| UpPTS                                | DwPTS                               | 75                    | 11.25                  |

| UpPTS                                | TS0                                 | 150                   | 22.5                   |

| TS1                                  | DwPTS                               | 200                   | 30                     |

| TS1                                  | TS0                                 | 275                   | 41.25                  |

Allowed cell radius for the occurrence of the special UL - DL interference

#### [Explanation difference:]

For the high chip rate option there is no DwPTS – guard – UpPTS structure. Here, the UL time slots are following the DL time slots immediately. Thus, there is only one step in degree and quality of interference between DL and UL signals.

For the low chip rate option, it makes a difference in quality and degree whether the DwPTS or TS is interfered by the UpPTS or TS1. Hence the trade-off between cell range and interference is more manifold for the low chip rate option.

### 4.4 Handover and Cell selection/reselection

The low chip rate TDD option should support the handover between UTRA modes (e.g, low chip rate TDD to high chip rate TDD, low chip rate TDD to FDD), and between systems (e.g. low chip rate TDD to GSM, etc.).

### 4.5 Particular characteristics of the low chip rate TDD

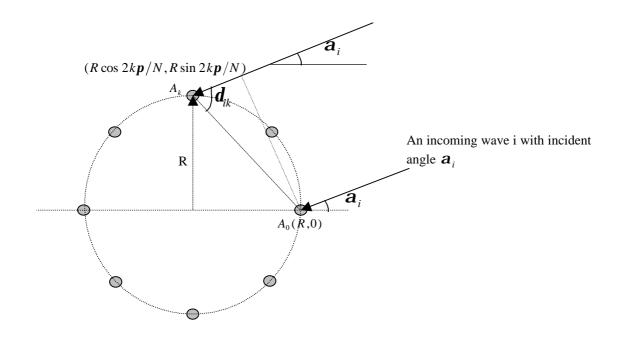

The features of uplink synchronization, smart antenna (beam forming) etc. have been discussed. These features were agreed to be included in this technical report as they may provide potential perfomance improvement.

# 5 High level characteristics

| Parameter/Feature          | Value/Expression                                                                                          | Note              |

|----------------------------|-----------------------------------------------------------------------------------------------------------|-------------------|

| Chip rate                  | 1.28 Mcps                                                                                                 |                   |

| Modulation                 | QPSK (8PSK)                                                                                               |                   |

| Spreading Factor           | 1/2/4/8/16                                                                                                |                   |

| Nominal Channel Spacing    | 1.6MHz / Carrier                                                                                          |                   |

| Burst Format               | 1 burst type                                                                                              |                   |

| Radio Frame Length         | 10ms (divided into 2 sub-frames)                                                                          |                   |

| Sub-frame length           | 5ms                                                                                                       |                   |

| Time slot number (traffic) | 7                                                                                                         |                   |

| Time slot length (us)      | 675                                                                                                       |                   |

| Downlink pilot slot (us)   | 75                                                                                                        | DwPTS             |

| Uplink pilot slot (us)     | 125                                                                                                       | UpPTS             |

| Guard Period (us)          | 75                                                                                                        | GP After<br>DwPTS |

| Range of uplink slot       | 1 – 6                                                                                                     |                   |

| Range of downlink slot     | 1 – 6                                                                                                     |                   |

| Receiver type              | Multi-user Detection (option), Rake                                                                       |                   |

| Pilot aided detection      | DwPTS, UpPTS, Midamble                                                                                    |                   |

| Synchronization aspect     | Downlink and uplink synchronization                                                                       |                   |

| Precision for UL sync.     | 1/8 chip                                                                                                  |                   |

| Antenna processing         | Smart antenna with beam forming                                                                           | Option            |

| Switching point            | Two switching points / sub-frame                                                                          |                   |

| Power control / rate       | Open loop power control                                                                                   |                   |

|                            | Closed loop power control / 200Hz (max rate)                                                              |                   |

| Variable bit rate service  | Supported (using TFCI)                                                                                    |                   |

| Basic resource unit        | One code, one slot with Spreading factor =16<br>(use of same resource in both consecutive sub-<br>frames) |                   |

| Service mapping            | Multi-code, multi-slot combination (variable spreading factor)                                            |                   |

| Interleaving period        | 10/20/40/80ms                                                                                             |                   |

| HO capability              | Low chip rate TDD to High chip rate TDD, FDD, GSM, etc.                                                   |                   |

| Tx Diversity | same capability as high chip rate TDD for<br>DwPTS,DPCH, but not for P-CCPCH; the<br>TxDiversity scheme used for the DPCH is used<br>for the FPACH, as well. | Refer to<br>sub clause<br>10.5 of TR |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|

### 6 Physical layer - General description

### 6.1 General description of Layer 1

Common with the high chip rate TDD mode

### 6.1.2 Service provided to higher layers

The physical layer offers data transport services to higher layers. The access to these services is through the use of transport channels via the MAC sub-layer. In addition to the functions listed in TS25.201, the physical layer for the low chip rate TDD option is expected to perform the following functions in order to provide the data transport service:

- beamforming

- synchronisation shift control

### 6.2 Document structure of the physical layer specification

### 6.2.1 Multiple Access

In contrast to the high chip rate TDD option, the access scheme is Direct-Sequence Code Division Multiple Access (DS-CDMA) with information spread over approximately 1.6 MHz bandwidth only, thus also often denoted as low chip rate TDD option due that nature.

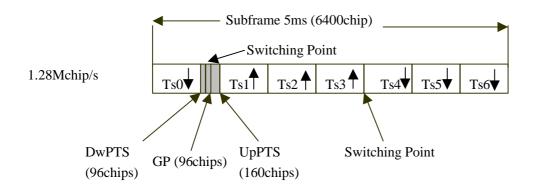

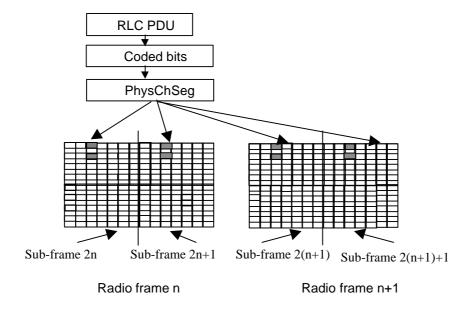

The frame structure of the low chip rate options differs from the high chip rate option in the following way: A 10 ms radio frame is divided into 2 sub-frames of 5ms. The frame structure (e.g. switching points) for each sub-frame in the 10ms frame length is the same. The sub-frame is divided into 7 traffic slots (864 chip/slot at the chip rate 1.28 Mcps) as described in subclause 7.2.1 'Frame Structure' and 3 timeslots with special functionality.

The information rate of the channel is different from the high chip rate option and varies with the symbol rate being derived from the 1.28 Mcps chip rate, the spreading factor and the modulation mode.

### 6.2.2 Channel coding and interleaving

Common with the high chip rate TDD mode

### 6.2.3 Modulation and spreading

The ordinary modulation scheme is QPSK, as for the high chip rate option. In addition to that 8PSK is also possible.

For separating different cells the following solutions are additionally supported in the low chip rate option:

- SYNC sequences, SYNC1 sequences.

For separating different UEs the following code families are additionally defined:

- SYNC1 sequences

### 6.2.4 Physical layer procedures

There are several physical layer procedures involved with low chip rate TDD operation that are different and in addition to the high chip rate option. Such procedures covered by physical layer description are:

- 1) The power control, for low chip rate TDD mode close loop control in both uplink and downlink.

- 2) Cell search operation.

- 3) Uplink synchronisation for low chip rate TDD mode.

- 4) Random access

- 5) Beamforming (optional)

### 6.2.5 Physical layer measurements

Common with the high chip rate TDD mode

#### [Explanation difference to section 6]

Most of the physical characters of the low chip rate TDD option are same as the high chip rate TDD option. But due to the different operation frequency band width and some other different implementation consideration such as power control method, uplink synchronization, there still exist some difference and all these differences will be discussed in the main part of TR25.928.

# 7 Physical channels and mapping of transport channels onto physical channels

### 7.1 Transport channels

### 7.1.1 Transport channels

'Common with the high chip rate TDD mode'

### 7.2 Physical channels

### 7.2.1 Frame structure

[Description:]

For low chip rate option, the frame length is 10ms and the 10ms frame is divided into 2 sub-frames of 5ms. The frame structure for each sub-frame in the 10ms frame length is the same.

The frame structure for each sub-frame is shown in Figure above.

Figure Structure of the sub-frame for low chip rate option

Tsn (n from 0 to 6): the nth normal time slot, 864 chips duration;

DwPTS: downlink pilot time slot, 96 chips duration;

UpPTS: uplink pilot time slot, 160 chips duration;

GP: main guard period for TDD operation, 96 chips duration;

#### [Rationale:]

In the figure above, the total number of normal traffic time slot for uplink and downlink is 7, and the length for each normal time slot is 864 chips duration. Among the 7 normal traffic time slot, Ts0 is always allocated as downlink while Ts1 is always allocated as uplink. The time slots for the uplink and the downlink

are separated by a switching point. Between the downlink time slots and uplink time slots, the special period is the switching point to separate the uplink and downlink. In each sub-frame of 5ms for low chip rate option, there are two switching points (uplink to downlink and vice versa). The proposed frame structure has taken some new technologies into consideration, either the smart antenna (beam forming) technology or the uplink synchronisation will be well supported.

Using the above frame structure, the low chip rate TDD option can operate on both symmetric and asymmetric mode by properly configuring the number of downlink and uplink time slots; (note that whatever the time slot configuration will be, the GP and DwPTS position within the frame should not change in order not to desynchronise the UEs and in order to allow Node B on air synchronisation procedures which make use of the DwPTS channel!) . It should be noted that in asymmetric operation mode, at least one normal uplink time slot and one downlink time slot will be allocated for traffic (Ts0 for downlink and Ts1 for uplink). The guard period GP of 96 chips can support the cell radius of up to about 11 km for uplink synchronization operation where the uplink transmission is advanced in macro-, micro- and pico- cell of small cells in cities or large cells in rural areas. Here the GP insures that an UE transmitting the UpPTS does not disturb the reception of the DwPTS for other UEs being close by. If this distortion is accepted in the network the cell radius can be bigger. (Note that the UpPTS is not continuously transmitted and the DwPTS is not continuously received.)

The only difference to the last version of the frame structure proposal for low chip rate is the improving of the numbering of the time slots. The physical layer behaviour does not change.

#### [Explanation of difference:]

For both high chip rate option and low chip rate option, the frame length is 10 ms, But for low chip rate option the 10 ms length is divided into 2 sub-frame of 5 ms to allow the fast update of power control, uplink synchronization, and smart antenna beamforming.

For high chip rate option , each 10 ms frame consists of 15 time slots, each allocated to either the uplink or the downlink . So it has both single and multiple-switching point configuration both for symmetric and asymmetric allocation. While in the low chip rate option, the position of the big Guard Period GP and of the DwPTS and UpPTS physical channels, is always between Ts0 and Ts1 whatever the level of asymmetry be.

### 7.2.2 Dedicated physical channel (DPCH)

### 7.2.2.1 Spreading

'Common with the high chip rate TDD mode'

### 7.2.2.2 Burst Types

[Description:]

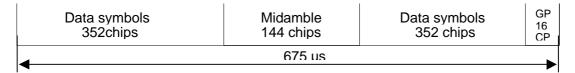

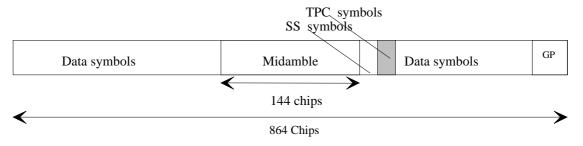

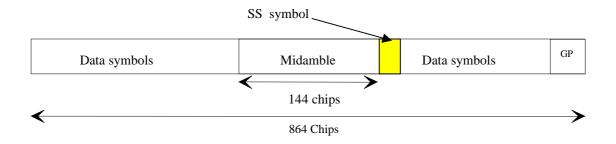

In correspondence to the frame structure described above, the burst structures for Tsn, DwPTS and UpPTS are proposed. The burst structure for normal time slot (Tsn) is described in Figure below.

Figure Burst structure for normal traffic time slot

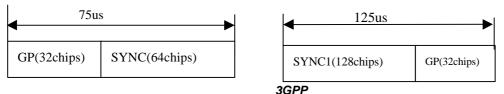

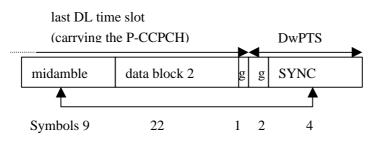

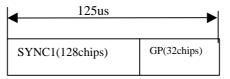

The structure for DwPTS and UpPTS is described in Figures below.

Figure Structure for DwPTS

Figure Structure for UpPTS

[Rationale:]

In the burst structure figure, the data symbols in each side of the midamble are 352 chips. The TPC bits for power control, the TFCI bits and the additional uplink synchronization bits (synchronization shift) are included in the Data symbols fields of the burst if they are needed. The amount of TFCI bits used is depending on the service and the details for TFCI, synchronization shift and TPC bits should be provided later with service mapping. For the power control symbols, the uplink synchronization control symbols and the TFCI the symbols around the midamble are used.

The GP field in the same figure for each time slot is used for protection between time slots to avoid the long delay multi-path interference. It should be noted that the GP of the TS0 together with the guard period in DwPTS is 48 chips long which is different with other normal guard period of 16 chips between time slots. This 'super long' guard period can be used to avoid the interference between the last normal downlink time slot and the downlink synchronization pilot burst. Otherwise, the interference to the last downlink time slot from the strong powered pilot will be serious to the traffic; and vice versa, the interference to the downlink pilot burst from the last downlink time slot will decrease the performance on downlink synchronization and cell search. Note that if the UEs serving Node B is far away and the UE makes handover measurements it will receive the beginning of the DwPTS of a close by Node B inside these 48 chip. 48 chip corresponds to 11 km difference in distance to the Node B. If the other Node B is more distant to the serving Node B, big guard period can be used for receiving the DwPTS of the handover candidate Node B.

In DwPTS and UpPTS, the content of SYNC and SYNC1 field are used for downlink and uplink pilot. The GP fields are used to separate the downlink (uplink) pilot from the normal downlink (uplink) time slot.

It should be pointed out that the uplink synchronization burst (SYNC1) is not followed by a RACH immediately. First the UL synchronization burst UpPTS is sent by the UE. This UpPTS is used for Node B to determine the received power level and the received timing. Second, the Node B transmits timing and power control information to the UE using the FPACH (one burst message) within the next 4 frames. Then the P-RACH is transmitted. Both FPACH and P-RACH are carrying single burst messages transmitted on a normal traffic time slot (see Burst structure figure). This two phase procedure which is different with the GSM of one phase procedure has better performance than the classical approach as used in GSM. In this case, the normal traffic burst and access burst can be active in the same time slot and the interference is reduced for each other if they are time-aligned.

Note that the UpPTS has to be transmitted by the UE in advance (staring in the big GP) to arrive at the Node B at the position indicated in the burst structure figure. The UpPTS can also be received at a different position if the UE cannot or does not aim at the RX position indicated in the burst structure figure. Thus, the UpPTS can also start within the guard interval (RX, TX), depending on the situation in the system. This means relaxation to estimate timing in UE, e.g. from pathloss on P-CCPCH.

And the proposed frame structure can support all the environments of macro-, micro- and pico- cells. In vehicular environment, the speed can be more than 120km/h. Also in the proposed frame structure, some specific properties for low chip rate option such as smart antenna technology, uplink synchronisation, beamforming, etc can be well supported.

#### [Explanation difference:]

In high chip rate option, there are 2 burst types of DPCH. They have different midamble lengths. And there is only one burst type of DPCH in the low chip rate option. The use of the same burst structure for RACH and for traffic will guarantee that the RACH can be handled with conventional traffic on the same UL time slots since the RACH is already UL synchronised.

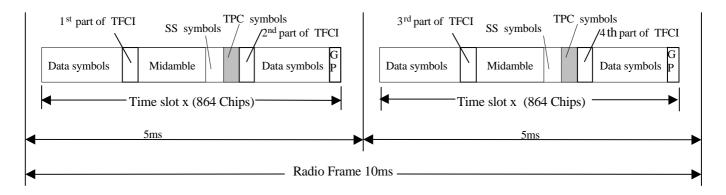

### 7.2.2.2.1 Transmission of TFCI

[Description:]

There is only one burst type for normal time slot in the low chip rate option. It provides the possibility for transmission of TFCI both in up- and downlink. For every user the TFCI information is to be transmitted

once per 10ms radioframe. If no TPC and SS are applied, the TFCI information is to be transmitted directly adjacent to the midamble of the 5ms subframe of the assigned frame. The position in case of TPC and/or SS application is shown in the figures below.

#### [Rationale:]

There is only one burst type for normal time slot in the low chip rate option. It provides the possibility for transmission of TFCI both in up- and downlink. For every user the TFCI information is to be transmitted once per 10ms radioframe. The transmission of TFCI is negotiated at call setup and can be re-negotiated during the call. For each CCTrCH it is indicated by higher layer signalling, which TFCI format is applied. Additionally for each allocated timeslot it is signalled individually whether that timeslot carries the TFCI or not. If a time slot contains the TFCI, then it is always transmitted using the first allocated channelisation

#### Position of TFCI information in the traffic burst in case of L1 control signals

code in the timeslot, according to the order in the higher

layer allocation message. The transmission of TFCI is done in the data parts of the respective physical channel, this means TFCI and data bits are subject to the same spreading procedure. The encoded TFCI symbols are both equally distributed between the subframes and between the data blocks. Hence the midamble structure and length is not changed. If no TPC and SS are applied, the TFCI information is to be transmitted directly adjacent to the midamble of the 5ms subframe of the assigned frame. The position in case of TPC and/or SS application is shown in the figures above. Figure above shows the position of the TFCI in a traffic burst, if L1 control signals, SS (synchronization shift) and TPC (Transmit Power Control), is transmitted.

#### [Explanation difference:]

In high chip rate option, both burst types 1 and 2 provide the possibility for transmission of TFCI both in upand downlink. The TFCI information is to be transmitted directly adjacent to the midamble if no TPC is transmitted. In the low chip rate option, there is only one burst type for normal time slot. It provides the possibility for transmission of TFCI both in up- and downlink. For every user the TFCI information is to be transmitted once per 10ms radioframe. The TFCI information is to be transmitted directly adjacent to the midamble of the 5ms subframe of the assigned frame if no TPC and SS is applied. The position of the TFCI in case of TPC and/or SS transmission is analogous to the high chiprate option and depicted in figure above.

#### 7.2.2.2.2 Transmission of TPC

#### [Description:]

There is only one burst type for normal time slot in the low chip rate option. It provides the possibility for transmission of L1 control signal "TPC" both in up- and downlink. For every user the TPC information is to be transmitted once per 5ms subframe.

#### [Rational:]

Hence the midamble structure and length is not changed. The TPC information is to be transmitted directly after SS. Figure below shows the position of the TPC in a traffic burst.

Figure : Position of TPC information in the traffic burst

For the number of layer 1 symbols there are 3 possibilities configurable for each channelisation code during the call setup:

- one SS and TPC symbol

- no SS and TPC symbols

- 16/SF SS and 16/SF TPC symbols (note: there is a need to study this further)

#### [Explanation difference:]

In high chip rate option, both burst types 1 and 2 provide the possibility for transmission of TPC only in uplink.

While in the low chip rate option, there is only one burst type for normal time slot. For the number of layer 1 symbols there are 3 possibilities configurable for each channelisation code during the call setup. It provides the possibility for transmission of TPC both in up- and downlink. For every user the TPC information is to be transmitted once per 5ms subframe. So it gives faster power control functionality in the low chip rate option than it does in high chip rate option. This is advantageous, because the lower chip rate has less frequency diversity which can be compensated with faster control algorithms. The smart antenna feature increases the demand on the speed of the control algorithms, because the smart antenna algorithms tend to focus on one DOA which has more Rayleigh fading than all DOAs received at a single antenna.

Note: This is to be verified by performance analysis

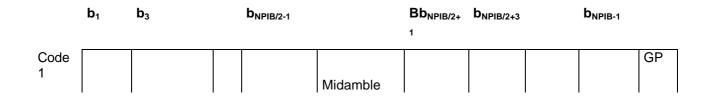

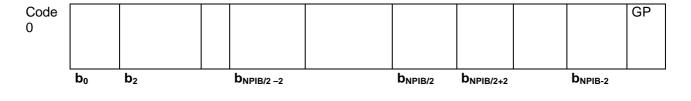

### 7.2.2.2.3 Timeslot formats

[Description:]

The timeslot format depends on the spreading factor, midamble length, the TPC and SS signals presence and on the number of the TFCI bits. In the case that L1 signals is used, different amount of bits are mapped to the two data fields. For the transmission of the TPC/SS, there are three possible configurations for the number of TPC/SS symbols:

- 1.1 symbol TPC and 1 symbol SS

- 2. No TPC and No SS.

- 3. 16/SF symbol TPC and 16/SF symbol SS.

So, in case 3, when SF=1, the number of TPC/SS is 16 symbol corresponding 32 bits (for QPSK) and 48 bits (for 8PSK).

16/SF TPC/SS symbols is for the case that the number of L1 signalling bits of one given RU after spreading are same although different SFs are used. Thus, the mapping of user data on the payload can stay the same regardless what the spreading factor is.

The timeslot formats are depicted in the following subclause.

7.2.2.3.1 Timeslot formats for Downlink

Table : Time slot formats for the Downlink

| Slot Format<br># | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | N <sub>SS</sub> & N <sub>TPC</sub><br>(bits) | Bits/slot | N <sub>Data/Slot</sub><br>(bits) | N <sub>data/data</sub><br><sub>field(1)</sub> (bits) | N <sub>data/data</sub><br><sub>field(2)</sub> (bits) |

|------------------|---------------------|-------------------------------|--------------------------|----------------------------------------------|-----------|----------------------------------|------------------------------------------------------|------------------------------------------------------|

| 0                | 16                  | 144                           | 0                        | 0&0                                          | 88        | 88                               | 44                                                   | 44                                                   |

| 1                | 16                  | 144                           | 4                        | 0&0                                          | 88        | 84                               | 42                                                   | 42                                                   |

| 2                | 16                  | 144                           | 8                        | 0&0                                          | 88        | 80                               | 40                                                   | 40                                                   |

| 3                | 16                  | 144                           | 16                       | 0&0                                          | 88        | 72                               | 36                                                   | 36                                                   |

| 4                | 16                  | 144                           | 32                       | 0&0                                          | 88        | 56                               | 28                                                   | 28                                                   |

| 5                | 16                  | 144                           | 0                        | 2&2                                          | 88        | 84                               | 44                                                   | 40                                                   |

| 6                | 16                  | 144                           | 4                        | 2&2                                          | 88        | 80                               | 42                                                   | 38                                                   |

| 7                | 16                  | 144                           | 8                        | 2&2                                          | 88        | 76                               | 40                                                   | 36                                                   |

| 8                | 16                  | 144                           | 16                       | 2&2                                          | 88        | 68                               | 36                                                   | 32                                                   |

| 9                | 16                  | 144                           | 32                       | 2&2                                          | 88        | 52                               | 28                                                   | 24                                                   |

| 10               | 1                   | 144                           | 0                        | 0&0                                          | 1408      | 1408                             | 704                                                  | 704                                                  |

| 11               | 1                   | 144                           | 4                        | 0&0                                          | 1408      | 1404                             | 702                                                  | 702                                                  |

| 12               | 1                   | 144                           | 8                        | 0&0                                          | 1408      | 1400                             | 700                                                  | 700                                                  |

| Slot Format<br># | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | N <sub>SS</sub> & N <sub>TPC</sub><br>(bits) | Bits/slot | N <sub>Data/Slot</sub><br>(bits) | N <sub>data/data</sub><br><sub>field(1)</sub> (bits) | N <sub>data/data</sub><br><sub>field(2)</sub> (bits) |

|------------------|---------------------|-------------------------------|--------------------------|----------------------------------------------|-----------|----------------------------------|------------------------------------------------------|------------------------------------------------------|

| 13               | 1                   | 144                           | 16                       | 0&0                                          | 1408      | 1392                             | 696                                                  | 696                                                  |

| 14               | 1                   | 144                           | 32                       | 0&0                                          | 1408      | 1376                             | 688                                                  | 688                                                  |

| 15               | 1                   | 144                           | 0                        | 2&2                                          | 1408      | 1404                             | 704                                                  | 700                                                  |

| 16               | 1                   | 144                           | 4                        | 2 & 2                                        | 1408      | 1400                             | 702                                                  | 698                                                  |

| 17               | 1                   | 144                           | 8                        | 2 & 2                                        | 1408      | 1396                             | 700                                                  | 696                                                  |

| 18               | 1                   | 144                           | 16                       | 2 & 2                                        | 1408      | 1388                             | 696                                                  | 692                                                  |

| 19               | 1                   | 144                           | 32                       | 2&2                                          | 1408      | 1372                             | 688                                                  | 684                                                  |

| 20               | 1                   | 144                           | 0                        | 32 & 32                                      | 1408      | 1344                             | 704                                                  | 640                                                  |

| 21               | 1                   | 144                           | 4                        | 32 & 32                                      | 1408      | 1340                             | 702                                                  | 638                                                  |

| 22               | 1                   | 144                           | 8                        | 32 & 32                                      | 1408      | 1336                             | 700                                                  | 636                                                  |

| 23               | 1                   | 144                           | 16                       | 32 & 32                                      | 1408      | 1328                             | 696                                                  | 632                                                  |

| 24               | 1                   | 144                           | 32                       | 32 & 32                                      | 1408      | 1312                             | 688                                                  | 624                                                  |

23

7.2.2.3.2 Timeslot formats for Uplink

Table : Time slot formats for the Uplink

| Slot Format | Spreading |                   | N <sub>TFCI</sub> (bits) | N <sub>SS</sub> & N <sub>TPC</sub> | Bits/slot | N <sub>Data/Slot</sub> | N <sub>data/data</sub>     | N <sub>data/data</sub>     |

|-------------|-----------|-------------------|--------------------------|------------------------------------|-----------|------------------------|----------------------------|----------------------------|

| #           | Factor    | length<br>(chips) |                          | (bits)                             |           | (bits)                 | <sub>field(1)</sub> (bits) | <sub>field(2)</sub> (bits) |

3G TR 25.928 V1.0.0 (2000-06)

| Slot Format<br># | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | N <sub>SS</sub> & N <sub>TPC</sub><br>(bits) | Bits/slot | N <sub>Data/Slot</sub><br>(bits) | N <sub>data/data</sub><br><sub>field(1)</sub> (bits) | N <sub>data/data</sub><br><sub>field(2)</sub> (bits) |

|------------------|---------------------|-------------------------------|--------------------------|----------------------------------------------|-----------|----------------------------------|------------------------------------------------------|------------------------------------------------------|

| 0                | 16                  | 144                           | 0                        | 0 & 0                                        | 88        | 88                               | 44                                                   | 44                                                   |

| 1                | 16                  | 144                           | 4                        | 0&0                                          | 88        | 84                               | 42                                                   | 42                                                   |

| 2                | 16                  | 144                           | 8                        | 0&0                                          | 88        | 80                               | 40                                                   | 40                                                   |

| 3                | 16                  | 144                           | 16                       | 0&0                                          | 88        | 72                               | 36                                                   | 36                                                   |

| 4                | 16                  | 144                           | 32                       | 0&0                                          | 88        | 56                               | 28                                                   | 28                                                   |

| 5                | 16                  | 144                           | 0                        | 2&2                                          | 88        | 84                               | 44                                                   | 40                                                   |

| 6                | 16                  | 144                           | 4                        | 2&2                                          | 88        | 80                               | 42                                                   | 38                                                   |

| 7                | 16                  | 144                           | 8                        | 2&2                                          | 88        | 76                               | 40                                                   | 36                                                   |

| 8                | 16                  | 144                           | 16                       | 2&2                                          | 88        | 68                               | 36                                                   | 32                                                   |

| 9                | 16                  | 144                           | 32                       | 2&2                                          | 88        | 52                               | 28                                                   | 24                                                   |

| 10               | 8                   | 144                           | 0                        | 0 & 0                                        | 176       | 176                              | 88                                                   | 88                                                   |

| 11               | 8                   | 144                           | 4                        | 0&0                                          | 176       | 172                              | 86                                                   | 86                                                   |

| 12               | 8                   | 144                           | 8                        | 0&0                                          | 176       | 168                              | 84                                                   | 84                                                   |

| 13               | 8                   | 144                           | 16                       | 0&0                                          | 176       | 160                              | 80                                                   | 80                                                   |

| 14               | 8                   | 144                           | 32                       | 0&0                                          | 176       | 144                              | 72                                                   | 72                                                   |

| 15               | 8                   | 144                           | 0                        | 2&2                                          | 176       | 172                              | 88                                                   | 84                                                   |

### 3G TR 25.928 V1.0.0 (2000-06)

| Slot Format<br># | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | N <sub>SS</sub> & N <sub>TPC</sub><br>(bits) | Bits/slot | N <sub>Data/Slot</sub><br>(bits) | N <sub>data/data</sub><br><sub>field(1)</sub> (bits) | N <sub>data/data</sub><br><sub>field(2)</sub> (bits) |

|------------------|---------------------|-------------------------------|--------------------------|----------------------------------------------|-----------|----------------------------------|------------------------------------------------------|------------------------------------------------------|

| 16               | 8                   | 144                           | 4                        | 2&2                                          | 176       | 168                              | 86                                                   | 82                                                   |

| 17               | 8                   | 144                           | 8                        | 2&2                                          | 176       | 164                              | 84                                                   | 80                                                   |

| 18               | 8                   | 144                           | 16                       | 2&2                                          | 176       | 156                              | 80                                                   | 76                                                   |

| 19               | 8                   | 144                           | 32                       | 2&2                                          | 176       | 140                              | 72                                                   | 68                                                   |

| 20               | 8                   | 144                           | 0                        | 4 & 4                                        | 176       | 168                              | 88                                                   | 80                                                   |

| 21               | 8                   | 144                           | 4                        | 4 & 4                                        | 176       | 164                              | 86                                                   | 78                                                   |

| 22               | 8                   | 144                           | 8                        | 4 & 4                                        | 176       | 160                              | 84                                                   | 76                                                   |

| 23               | 8                   | 144                           | 16                       | 4 & 4                                        | 176       | 152                              | 80                                                   | 72                                                   |

| 24               | 8                   | 144                           | 32                       | 4 & 4                                        | 176       | 136                              | 72                                                   | 64                                                   |

| 25               | 4                   | 144                           | 0                        | 0&0                                          | 352       | 352                              | 176                                                  | 176                                                  |

| 26               | 4                   | 144                           | 4                        | 0&0                                          | 352       | 348                              | 174                                                  | 174                                                  |

| 27               | 4                   | 144                           | 8                        | 0&0                                          | 352       | 344                              | 172                                                  | 172                                                  |

| 28               | 4                   | 144                           | 16                       | 0&0                                          | 352       | 336                              | 168                                                  | 168                                                  |

| 29               | 4                   | 144                           | 32                       | 0&0                                          | 352       | 320                              | 160                                                  | 160                                                  |

| 30               | 4                   | 144                           | 0                        | 2&2                                          | 352       | 348                              | 176                                                  | 172                                                  |

| 31               | 4                   | 144                           | 4                        | 2&2                                          | 352       | 344                              | 174                                                  | 170                                                  |

| 32               | 4                   | 144                           | 8                        | 2&2                                          | 352       | 340                              | 172                                                  | 168                                                  |

25

| Slot Format<br># | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | N <sub>SS</sub> & N <sub>TPC</sub><br>(bits) | Bits/slot | N <sub>Data/Slot</sub><br>(bits) | N <sub>data/data</sub><br><sub>field(1)</sub> (bits) | N <sub>data/data</sub><br><sub>field(2)</sub> (bits) |

|------------------|---------------------|-------------------------------|--------------------------|----------------------------------------------|-----------|----------------------------------|------------------------------------------------------|------------------------------------------------------|

| 33               | 4                   | 144                           | 16                       | 2&2                                          | 352       | 332                              | 168                                                  | 164                                                  |

| 34               | 4                   | 144                           | 32                       | 2&2                                          | 352       | 316                              | 160                                                  | 156                                                  |

| 35               | 4                   | 144                           | 0                        | 8&8                                          | 352       | 336                              | 176                                                  | 160                                                  |

| 36               | 4                   | 144                           | 4                        | 8&8                                          | 352       | 332                              | 174                                                  | 158                                                  |

| 37               | 4                   | 144                           | 8                        | 8&8                                          | 352       | 328                              | 172                                                  | 156                                                  |

| 38               | 4                   | 144                           | 16                       | 8&8                                          | 352       | 320                              | 168                                                  | 152                                                  |

| 39               | 4                   | 144                           | 32                       | 8 & 8                                        | 352       | 304                              | 160                                                  | 144                                                  |

| 40               | 2                   | 144                           | 0                        | 0&0                                          | 704       | 704                              | 352                                                  | 352                                                  |

| 41               | 2                   | 144                           | 4                        | 0&0                                          | 704       | 700                              | 350                                                  | 350                                                  |

| 42               | 2                   | 144                           | 8                        | 0&0                                          | 704       | 696                              | 348                                                  | 348                                                  |

| 43               | 2                   | 144                           | 16                       | 0&0                                          | 704       | 688                              | 344                                                  | 344                                                  |

| 44               | 2                   | 144                           | 32                       | 0&0                                          | 704       | 672                              | 336                                                  | 336                                                  |

| 45               | 2                   | 144                           | 0                        | 2&2                                          | 704       | 700                              | 352                                                  | 348                                                  |

| 46               | 2                   | 144                           | 4                        | 2&2                                          | 704       | 696                              | 350                                                  | 346                                                  |

| 47               | 2                   | 144                           | 8                        | 2 & 2                                        | 704       | 692                              | 348                                                  | 344                                                  |

| 48               | 2                   | 144                           | 16                       | 2 & 2                                        | 704       | 684                              | 344                                                  | 340                                                  |

| 49               | 2                   | 144                           | 32                       | 2 & 2                                        | 704       | 668                              | 336                                                  | 332                                                  |

26

3G TR 25.928 V1.0.0 (2000-06)

| Slot Format<br># | Spreading<br>Factor | Midamble<br>length<br>(chips) | N <sub>TFCI</sub> (bits) | N <sub>SS</sub> & N <sub>TPC</sub><br>(bits) | Bits/slot | N <sub>Data/Slot</sub><br>(bits) | N <sub>data/data</sub><br><sub>field(1)</sub> (bits) | N <sub>data/data</sub><br><sub>field(2)</sub> (bits) |

|------------------|---------------------|-------------------------------|--------------------------|----------------------------------------------|-----------|----------------------------------|------------------------------------------------------|------------------------------------------------------|

| 50               | 2                   | 144                           | 0                        | 16 & 16                                      | 704       | 672                              | 352                                                  | 320                                                  |

| 51               | 2                   | 144                           | 4                        | 16 & 16                                      | 704       | 668                              | 350                                                  | 318                                                  |

| 52               | 2                   | 144                           | 8                        | 16 & 16                                      | 704       | 664                              | 348                                                  | 316                                                  |

| 53               | 2                   | 144                           | 16                       | 16 & 16                                      | 704       | 656                              | 344                                                  | 312                                                  |

| 54               | 2                   | 144                           | 32                       | 16 & 16                                      | 704       | 640                              | 336                                                  | 304                                                  |

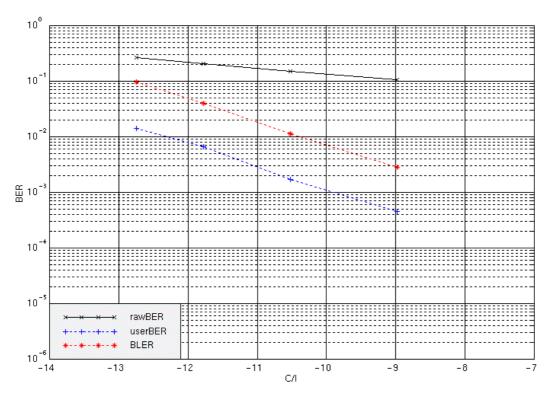

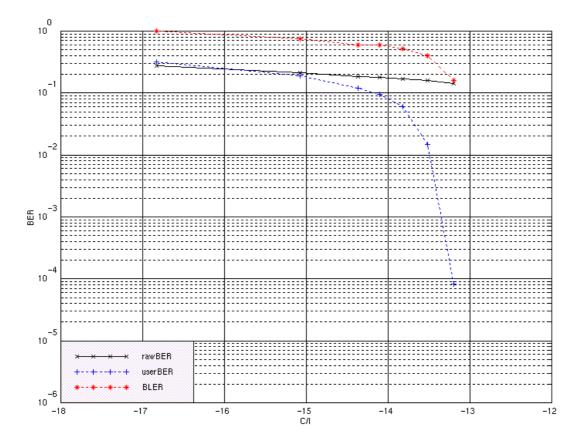

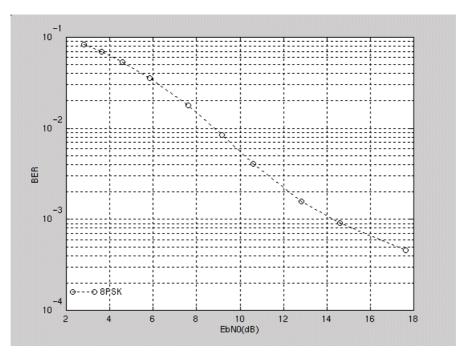

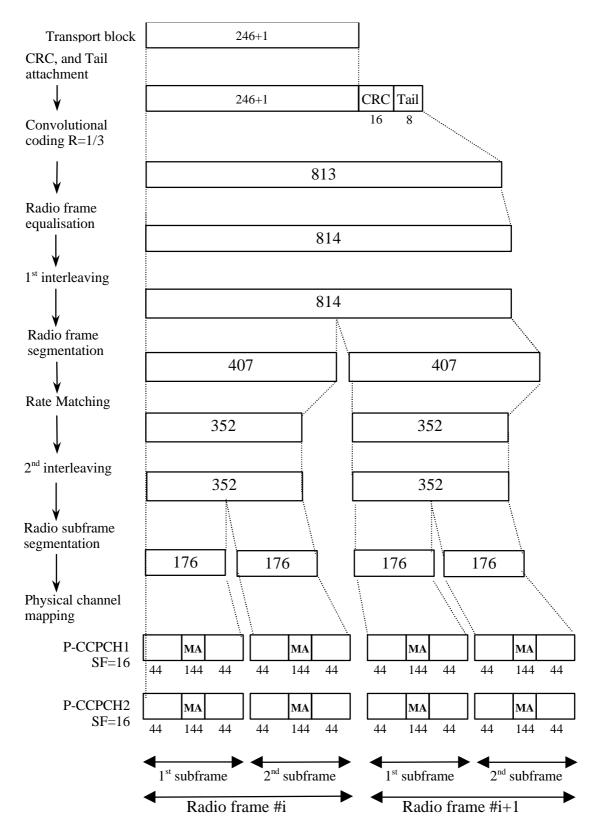

| 55               | 1                   | 144                           | 0                        | 0&0                                          | 1408      | 1408                             | 704                                                  | 704                                                  |