TSG-RAN Working Group 1 meeting No. 5 June 1-4, Cheju, Korea

| Agenda Item:  | Adhoc 12                                                                                                                 |

|---------------|--------------------------------------------------------------------------------------------------------------------------|

| Source:       | Siemens, Texas Instruments                                                                                               |

| Title:        | Generalised Hierarchical Golay Sequence for PSC with low complexity correlation using pruned efficient Golay correlators |

| Document for: | Discussion                                                                                                               |

### Abstract

In the last WG1 Meeting, two PSC schemes have been presented, namely the hierarchical correlation, which is the working assumption in S1.13 [1] (latest refinement according to[2]) and the Golay sequence (proposed by TI [3], [4]).

Both schemes allow an efficient computation of the correlation in the mobile station and have been shown to have good correlation properties. For the working assumption simulations under high frequency errors have already been presented [2].

In order to avoid lengthy arguments about marginal relative merits of these two PSC schemes we propose to combine their advantages in a harmonised proposal. That means we propose to use a hierarchical sequence, built from two length 16 constituent sequences, which can themselves be hierarchical sequences (sequence  $X_1$ ).  $X_2$  and the constituent sequences of  $X_1$  are Golay sequences. Alternatively, the proposed sequence can be viewed as pruned Golay code, because at some stages in the generation of a Golay code, one of the outputs is pruned and instead the other output is used as input for the next stage. The pruning of the Golay code gives it a hierarchical structure.

We show that this proposal has a lower complexity than each of the above mentioned PSC schemes while maintaining the synchronisation properties even under high frequency errors. We therefore suggest to use this harmonised approach for the PSC.

Such a selection of the PSC would also simplify the pending decision about the SSC scheme by narrowing down the number of necessary simulations to be considered, because the performance of a SSC scheme can only be judged in combination with a particular PSC scheme.

The paper is organised as follows:

- First we present the proposed PSC

- Second we show how it can be utilised for efficient correlation and show that the complexity is lower than for any of the previous proposal

- Third we present simulations results under no and high frequency error and show that there is almost no difference in slot synchronisation performance for the proposed code in comparison to the working assumption.

- Finally we propose this new PSC code to be used and provide a text proposal for S1.13

## **Generalised Hierarchical Golay Sequence**

For the 1<sup>st</sup> step of cell search procedure the working assumption is to use a hierarchical correlation sequence for the PSC code[1]. The code is generated by two constituent sequences, using the formula

$y(i) = X_2(i \mod 16) \cdot X_1(i \dim 16)$  for i = 0...255

Note that in this formula the elements of the binary sequences are assumed to be  $\{-1,+1\}$ . In [1] the formula is described equivalently assuming the elements of the binary sequences are  $\{+1,0\}$ . The multiplication is changed against exclusive or operation to achieve equivalent results.

We now propose to combine the advantages of the generalised hierarchical and the recursive Golay set-up in a harmonised way. That means we build the constituent length 16 sequence  $X_2$  as a (generalised) hierarchical sequence whose constituent sequences are again selected to be two (length 4) Golay sequences.  $X_1$  is selected to be a Golay sequence of length 16.

Obviously, selecting hierarchical sequences or Golay sequences again as the constituent sequences, a further saving in complexity can be achieved. However, we found it is necessary to somewhat generalise the definition of the hierarchical sequences (especially for the hierarchical sequence forming the constituent sequence  $X_2$ ) and to select the best suited parameters for the Golay sequences. This optimisation was done using a computer search.

The construction principle of the hierarchical sequences can be generalised. Up to now one of the constituent sequences was repeated in its full length, the repetitions were modulated with the value of the corresponding element of the other constituent sequence. We now generalise this and allow only the first half (or an other fraction, but we will actually use the half) to be repeated, followed by the second half and the repetitions there of. The repetitions are modulated with the other constituent sequence (in our case  $X_3$ ) as was the case for the non generalised hierarchical sequence. We introduce the parameter s which indicates the length of the constituent sequence part of  $X_4$  which is repeated as a single chunk.. The formula describing the generalised approach would be:

$X_{2}(i) = X_{4}(i \mod s + s \cdot (i \dim sn_{3})) \cdot X_{3}((i \dim s) \mod n_{3})$  for  $i = 0...n_{3} \cdot n_{4}$

The length of the sequence  $X_3$  and  $X_4$  is called  $n_3$ ,  $n_4$  respectively. Assuming  $s=n_4$  would give us again the standard hierarchical sequence.

We now propose to combine the advantages of the generalised hierarchical and the recursive Golay set-up in a harmonised way. That means we build the first constituent length 16 sequence  $X_1$  of the 256 chip hierarchical sequence from a Golay sequence. The second sequence  $X_2$  is a generalised hierarchical sequence whose constituent sequences are again selected to be two (length 4) Golay sequences  $X_3$  and  $X_4$ .

$X_1$  is defined to be the length 16 Golay sequence obtained by the delay matrix  $D^{(1)} = [8, 4, 1, 2]$ , the weight matrix  $W^{(1)} = [1, -1, 1, 1]$  and  $N^{(1)} = 4$ .

$X_2$  is a generalised hierarchical sequence using the formula above, selecting s=2 and using the two Golay sequences  $X_3$  and  $X_4$  as constituent sequences.  $X_3$  and  $X_4$  are defined to be identical and the length 4 Golay sequence obtained by the delay matrix  $D^{(3)} = D^{(4)} = [1, 2]$ , the weight matrix  $W^{(3)} = W^{(4)} = [1, 1]$  and  $N^{(3)} = N^{(4)} = 2$ .

Using the following recursive relation as explained in [3] and the weight matrix W<sup>(j)</sup>, the delay matrix D<sup>(j)</sup>, and N<sup>(j)</sup>

| $a_0(k) = \delta(k)$ and $b_0(k) = \delta(k)$                | (1) |

|--------------------------------------------------------------|-----|

| $a_n(k) = a_{n-1}(k) + W^{(j)}{}_n b_{n-1}(k - D^{(j)}{}_n)$ | (2) |

| $b_n(k) = a_{n-1}(k) - W_n^{(j)} b_{n-1}(k - D_n^{(j)}),$    | (3) |

$$k = 0, 1, 2, .2.**N^{(j)}-1,$$

$n = 1, 2, .N^{(j)}.$

gives the wanted Golay sequence  $X_j$  defined by  $a_n$  assuming  $n=N^{(j)}$ . The Kronecker delta function is described by  $\delta$ , k and n are intergers.

Alternatively, the sequence y can be viewed as a pruned Golay code and generated using the following parameters for equations (1-3):

- (a) Let j = 0,  $N^{(0)} = 8$

- (b)  $[D_1^0, D_2^0, D_3^0, D_4^0, D_5^0, D_6^0, D_7^0, D_8^0] = [128, 64, 16, 32, 8, 4, 1, 2]$

- (c)  $[W_1^0, W_2^0, W_3^0, W_4^0, W_5^0, W_6^0, W_7^0, W_8^0] = [1, -1, 1, 1, 1, 1, 1, 1]$

#### 3GPP/TSG/RAN/WG1#5 TDOC 554/99

(d) For n = 4, 6, set  $b_4(k) = a_4(k)$ ,  $b_6(k) = a_6(k)$ , where  $a_4(k)$ ,  $a_6(k)$  are given by equation (2).

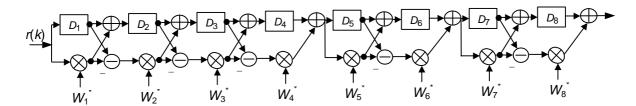

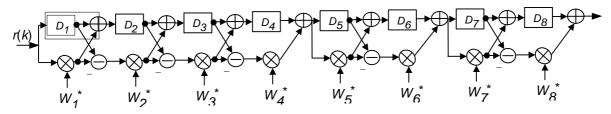

One possible implementation of the entire correlator could be as shown below, and it is called as the pruned efficient Golay correlator.

Figure 1: Pruned Efficient Golay Correlator for the generalised Hierarchical Golay sequence.

The elements  $D_1, D_2, ..., D_8$  are given by the delay matrix [128, 16, 64, 32, 8, 4, 1, 2] and respectively the weights are given by [1, -1, 1, 1, 1, 1, 1, 1]. This pruned efficient golay correlator only requires 13 adds per correlation output.

We name the code obtained from the working assumption  $S_{new}$  and the Generalised Hierarchical Golay code GHG for the rest of this paper. The latter offers in comparison to a code with plain Hierarchical or Golay based structure additional advantages due to a efficient calculation of correlation sum. Simulations will show, that there is now significant difference in slot synchronisation performance of the presently discussed PSC codes even in presence of a higher frequency error. The benefits of this proposal are as follows:

- all benefits of the hierarchical and Golay sequences are maintained

- The change can be regarded as a minor change in the constituent sequences X<sub>1</sub> and X<sub>2</sub>

- the 1<sup>st</sup> step of initial cell search can be executed more efficiently for the proposed code compared to the Hierarchical only or Golay only scheme

- there is no noticeable difference in slot synchronisation performance between S<sub>new</sub> and GHG.

## **Correlation properties**

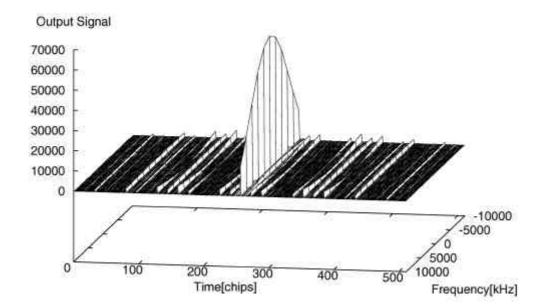

Figure 2: Output signal versus frequency and time for the Generalised Hierarchical Golay sequence.

Figure 2 shows the PSC simulation output signal using the Generalised Hierarchical Golay (GHG) sequence as described above assuming no additional noise no SSC and a channel transmission characteristic to be unity. The simulation output signal is obtained from the real part and the imaginary part of the signal after the PSC matched filter device (e.g. a pruned efficient Golay correlator structure) by computing the squared absolute value of the complex output signal. As can be easily seen the plot of the GHG sequence has low side correlation values in the whole frequency range of  $\pm 10$  kHz. The degradation of the side peaks is relative flat. Suppose for example a frequency error of 10 kHz. Then the ratio between maximum side correlation and the main peak is about -6 dB. The variance of maximum side correlation is obviously very small. The side correlation for no frequency error is about 12 dB lower than the maximum correlation peak.

# Complexity comparison of correlation sequences

The complexity of any correlation scheme depends heavily on the selected architecture and technology, so direct comparisons between schemes having a rather different construction principle are very difficult. Therefore it is probably impossible to tell unambiguously, whether the plain hierarchical or the plain Golay sequences show the lower complexity. Basically the Golay sequences need fewer adders while the hierarchical sequences allow a more regular implementation of the delay storage which favours a RAM implementation for an ASIC design. In the following we will compare the Generalised Hierarchical Golay sequences against both plain schemes and show they have at most the same complexity, but most likely have a lower complexity than any of the two plain schemes. While this analysis will not provide us with absolute figures (they are too heavily technology dependant) it has the advantage of being almost as convincing as a mathematical proof (but we wont take the burden to try to formulate it in a mathematical way).

#### Comparison against plain Hierarchical correlation scheme

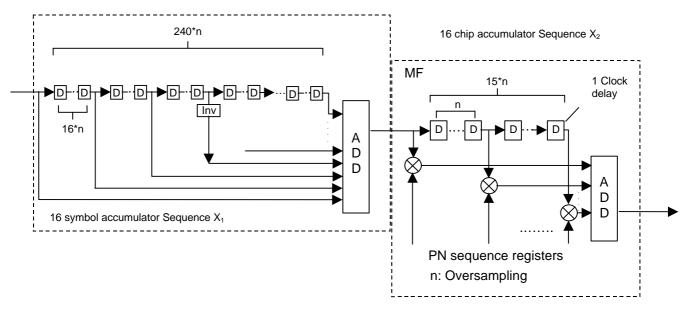

The following shows the general correlation scheme for the Hierarchical correlation:

Figure 3: Efficient Correlator for plain hierarchical sequence.

The Hierarchical correlation consists of two concatenated matched filter blocks, each performing a standard correlation over one of the constituent sequences. We assume that the correlation over  $X_1$  (16 symbol accumulation) is done before the correlation over  $X_2$  (16 chip accumulation). Note this is possible as an implementation option without changes to the standard, because both matched filter blocks (enclosed in dotted lines in the above figure) are linear systems which can be connected in either order. In this way, all the 240 \*n delay lines can be implemented with the minimum wordlength as no accumulation is done before no signal to interference gain is achieved.

The Hierarchical Golay sequence is still at the same time a Hierarchical sequence, so any hardware which is already designed can simply be reused for the Hierarchical Golay sequence. This can be done by simply changing the two constituent sequences although a more efficient solution is offered by the (generalised) Hierarchical approach as described above. This proves, that the new sequences have at most the same complexity as the current working assumption.

Reusing existing hardware may not be of prime importance for the commercial terminals to be used when the service is opened to the public, but it certainly eases the design of pre-commercial prototypes to be used in field trial systems and to check interworking with base station prototypes of various vendors to collect valuable experience for the final designs and to assure a smooth launch of the service afterwards.

As mentioned, if felt advantageous for the selected technology, one or both of the matched filter blocks can be replaced again by a (generalised) hierarchical sequence and by an Efficient Golay Correlator (EGC).

The complexity is then almost certainly smaller than for the plain hierarchical correlation. So almost certainly the complexity of the Hierarchical Golay correlation sequence will be lower than the correlation of the plain Hierarchical sequence.

#### Comparison against plain Golay correlation scheme

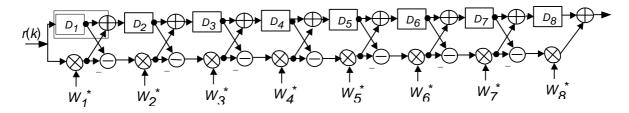

The following shows the general correlation scheme for the Efficient Golay correlator (EGC):

Figure 4: Efficient Golay Correlator for plain Golay sequence.

An efficient Hierarchical Golay correlator has the same configuration, except two adders can be omitted:

Figure 5: Pruned Efficient Golay Correlator (PEGC) for generalised Hierarchical Golay sequence.

Obviously, saving two adders out of 15 will bring down the complexity of the scheme accordingly. Further more, due to the structure of the hierarchical correlation which allows to apply other design optimisations alternatively or together with the EGC, the total saving for an optimised design will most likely be even higher.

## Simulation performance

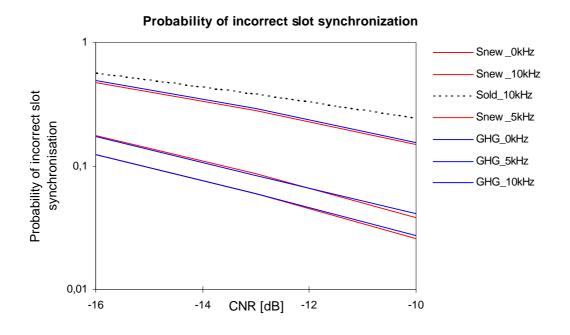

We have investigated the slot synchronisation step on a 3 km/h one ray Rayleigh fading channel for different chip to noise ratios (CNR) under no and high frequency error. We show that there is virtually no difference in slot synchronisation performance for the proposed GHG code in comparison to the working assumption  $S_{new}$ . We have results for using 24 slots averaging. Together with the PSC a secondary synchronisation channel is transmitted randomly chosen to be one of 32 symbols as described in [2]. The plot shows, that there is no significant difference between the current Hierarchical PSC code scheme  $S_{new}$  and the new generalised Hierarchical Golay proposal GHG for no frequency error 5 kHz frequency error and even a high frequency error of 10 kHz. Compared to the hierarchical code  $S_{old}$  proposed initially [7] all discussed PSC codes show better properties (especially in presence of higher frequency error). The proposed sequence has better autocorrelation properties in particular at 10 kHz than the previous working assumption  $S_{old}$  (broken curve). The plot suggests, that the synchronisation properties of GHG are practically optimal.

Figure 6: PSC Simulation results (together with the PSC a randomly chosen SSC is transmitted)

# Conclusion

We propose to use the generalised hierarchical Golay sequences to be used for the PSC in order to take advantage of the reduced computation complexity. The complexity will be reduced from 30 adds per output sample for the present working assumption to 13 adds only. This also outperforms the Golay sequences which would need 15 adds.

As shown by simulations the new PSC selection will still obtain the same performance under both low and high frequency errors. The new PSC scheme can be used together with all currently discussed SSC schemes. Due to a lower computational complexity less dedicated hardware is needed and a lower power consumption is achieved.

# References

- [1] S1.13 , Spreading and modulation (FDD) 3GPP TSG RAN W1 Tdoc 99-521

- [2] Siemens 'A new Hierarchical Correlation Sequence with good Properties in Presence of a Frequency Error'3GPP TSG RAN W1 Tdoc 99/146

- [3] Texas Instruments Reduced complexity primary and secondary synchronisation codes with good autocorrelation properties for the WCDMA system," 3GPP TSG RAN W1 Tdoc 99-373

- [4] Texas Instruments Further results on Golay codes based PSC and SSC," 3GPP TSG RAN W1 Tdoc 99-422

- [5] TS 25.213 V2.0.0 Spreading and modulation (FDD)

- [6] TS 25.223 V2.0.0 Spreading and modulation (TDD)

- [7] A new correlation sequence for the Primary Synchronisation Code with good correlation properties and low detector complexity, SMG2 UMTS-L1 TDOC 427/98