# TSG-RAN Working Group 1 meeting #10

Beijing, China

January 18 -21, 2000

Agenda item:

Source: Nokia

**Title:** CR 25212-030: Clarification on turbo internal interleaver

**Document for:** Decision

This CR introduces a clarification on the internal inteleaver section of TS 25.212. The functionality is not changed, only presentation is made more consistent.

This CR was distributed earlier as TS 25212-CR021rev1.

# 3GPP RAN WG1 Meeting #10 Beijing, China, 18 – 21 Jan 2000

# Document R1-00-0014

e.g. for 3GPP use the format TP-99xxx or for SMG, use the format P-99-xxx

| CHANGE REQUEST  Please see embedded help file at the bottom of this page for instructions on how to fill in this form correctly.                                                                                                                                               |                                                                                                                                                  |                                                                                                              |                                                                    |               |             |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------|-------------|--|--|

| GSM (AA.BB) or 3G (AA.BBB) sp                                                                                                                                                                                                                                                  |                                                                                                                                                  | CR 0                                                                                                         |                                                                    | Current Versi |             |  |  |

| For submission to: RAN #7 for approval Ist expected approval meeting # here for information for information strategic was only.  Form: CR cover sheet, version 2 for 3GPP and SMG The latest version of this form is available from: ftp://ftp.3gpp.org/Information/CR-Form-v2 |                                                                                                                                                  |                                                                                                              |                                                                    |               |             |  |  |

| Proposed change affects: (U)SIM ME X UTRAN / Radio X Core Network (at least one should be marked with an X)                                                                                                                                                                    |                                                                                                                                                  |                                                                                                              |                                                                    |               |             |  |  |

| Source: Nokia                                                                                                                                                                                                                                                                  |                                                                                                                                                  |                                                                                                              |                                                                    | Date:         | 13-Jan-2000 |  |  |

| Subject: Update                                                                                                                                                                                                                                                                | for 4.1.3.2.3 of 25.21                                                                                                                           | 2 for clarific                                                                                               | ation                                                              |               |             |  |  |

| Work item:                                                                                                                                                                                                                                                                     |                                                                                                                                                  |                                                                                                              |                                                                    |               |             |  |  |

| (only one category shall be marked C Function                                                                                                                                                                                                                                  | Corresponds to a correction in an earlier release  Release 96 Release 97 Corresponds to a correction in an earlier release Release 97 Release 98 |                                                                                                              |                                                                    |               |             |  |  |

| The current text explains the Turbo Code Internal Interleaver in a very complicated way.  The connection to 4.2.2.2 is missing, i.e., there is no text to describe how bits from 4.2.2.2 are interleaved in 4.1.3.2.3.                                                         |                                                                                                                                                  |                                                                                                              |                                                                    |               |             |  |  |

| Clauses affected: 4.                                                                                                                                                                                                                                                           | 1.3.2.3 of TS25.212                                                                                                                              |                                                                                                              |                                                                    |               |             |  |  |

| affected: Other GS speci MS test: BSS test                                                                                                                                                                                                                                     | Core specifications SM core ifications specifications specifications ecifications                                                                | $\begin{array}{c} \rightarrow \ L \\ \hline \rightarrow \ L \\ \hline \rightarrow \ L \\ \hline \end{array}$ | st of CRs:<br>st of CRs:<br>st of CRs:<br>st of CRs:<br>st of CRs: |               |             |  |  |

| Other comments:                                                                                                                                                                                                                                                                |                                                                                                                                                  |                                                                                                              |                                                                    |               |             |  |  |

<----- double-click here for help and instructions on how to create a CR.

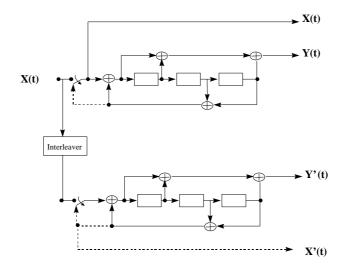

Figure 4: Structure of the 8 state PCCC encoder (dotted lines effective for trellis termination only)

The initial value of the shift registers of the PCCC encoder shall be all zeros.

The output of the PCCC encoder is punctured to produce coded bits corresponding to the desired code rate. For rate 1/3, none of the systematic or parity bits are punctured, and the output sequence is X(0), Y(0), Y'(0), X(1), Y(1),

### 4.2.3.2.2 Trellis termination for Turbo coding

Trellis termination is performed by taking the tail bits from the shift register feedback after all information bits are encoded. Tail bits are added after the encoding of information bits.

The first three tail bits shall be used to terminate the first constituent encoder (upper switch of figure 4 in lower position) while the second constituent encoder is disabled. The last three tail bits shall be used to terminate the second constituent encoder (lower switch of figure 4 in lower position) while the first constituent encoder is disabled.

The transmitted bits for trellis termination shall then be

$$X(t) Y(t) X(t+1) Y(t+1) X(t+2) Y(t+2) X'(t) Y'(t) X'(t+1) Y'(t+1) X'(t+2) Y'(t+2).$$

## 4.1.3.2.34.2.3.2.3 Turbo code internal interleaver

Figure  $5\underline{4}$  depicts the overall 8 state PCCC Turbo coding scheme including Turbo code internal interleaver. A length of a turbo code internal interleaver is allowed to take any value from 320 to 5114 inclusive assigned according to the rules described in 4.2.2.2. The length is denoted by  $K_i$  for a TrCH i. Elements of a turbo code internal interleaver are denoted by T(k),  $k = 1, 2, ..., K_i$ , and each of them stands for the original position of an k:th interleaved bit. The range of T(k) is  $1 \le T(k) \le K_i$ .

The bits input to the turbo code internal interleaver are denoted by  $o_{ir1}, o_{ir2}, o_{ir3}, \dots, o_{irK_i}$  and the bits after interleaving are denoted by  $x_{ir1}, x_{ir2}, x_{ir3}, \dots, x_{irK_i}$ , where i is a TrCH number and r is a code block number (for details see 4.2.2.2). The relationship between the two is defined by:  $x_{irk} = o_{irT(k)}$  for  $k = 1, 2, \dots, K_i$ .

Every interleaving index T(k) shall satisfy the following stepwise algorithm:

#### 4.2.3.2.3.1 Algorithm for turbo interleaver

The following section specific notation is used for the parameters in the algorithm:

| K                 | Length of Turbo Code Internal Interleaver for a TrCH |

|-------------------|------------------------------------------------------|

| <u>A</u>          | Number of rows of an A times B matrix                |

| В                 | Number of columns of an A times B matrix             |

| 1                 | Prime number                                         |

| m                 | Primitive root for <i>I</i>                          |

| ROP               | Row order pattern                                    |

| BR                | Base sequence                                        |

| Q                 | Minimum prime integer sequence                       |

| MIS               | Minimum row index sequence                           |

| i                 | Index in row dimension                               |

| j                 | Index in column dimension                            |

| $\underline{i_0}$ | Index in row dimension                               |

| <u>z</u>          | Candidate index for Turbo Code Internal Interleaver  |

|                   |                                                      |

1. Assign values for the number of rows A, the number of columns B, the prime number I, and the primitive root  $\underline{m}$  depending on K:

If 480 < K < 531 then

A = 10;

1 = 53;

B = 53;

m = 2;

<u>else</u>

A = 20;

find a least prime I such that  $K \le A*(I+1)$ ;

select B by

$$B = \begin{cases} \mathbf{l} - 1 & \text{if } K \leq A * (\mathbf{l} - 1), \\ \mathbf{l} & \text{if } A * (\mathbf{l} - 1) < K \leq A * \mathbf{l}, \\ \mathbf{l} + 1 & \text{if } A * \mathbf{l} < K \leq A * (\mathbf{l} + 1). \end{cases}$$

select **m** from Table 2 below on the right side of **1**.

endif

2. Select the row order pattern ROP out of Pattern<sub>1</sub>, Pattern<sub>2</sub>, and Pattern<sub>3</sub> depending on K:

K ROP

320 to 480: *Pattern*<sub>1</sub>; (inclusive)

481 to 530: *Pattern*<sub>3</sub>;

531 to 2280: *Pattern*<sub>1</sub>;

2281 to 2480: Pattern<sub>2</sub>;

2481 to 3160: Pattern<sub>1</sub>;

3161 to 3210: Pattern<sub>2</sub>;

3211 to 5114: *Pattern*<sub>1</sub>;

*Pattern<sub>1</sub>*: {19, 9, 14, 4, 0, 2, 5, 7, 12, 18, 10, 8, 13, 17, 3, 1, 16, 6, 15, 11}.

Pattern<sub>2</sub>: {19, 9, 14, 4, 0, 2, 5, 7, 12, 18, 16, 13, 17, 15, 3, 1, 6, 11, 8, 10}.

*Pattern*<sub>3</sub>: {9, 8, 7, 6, 5, 4, 3, 2, 1, 0}.

3. Construct the base sequence BR(j), j=0,1,2,..., I-2, by BR(0)=1 and

$$BR(j) = (m*BR(j-1)) \text{ modulo } l \text{ for } j = 1,2,..., l-2.$$

- 4. Select the minimum prime integer sequence Q(i), i=0,1,...,A-1, such that Q(0)=1 and gcd(Q(i),I-1)=1, Q(i)>6, and Q(i)>Q(i-1) for i=1,2,...,A-1. Here gcd(x,y) is the greatest common divisor of integers x and y.

- 5. Calculate the minimum row index sequence MIS(i), i=0,1,..., A-1, by

$$MIS(i) = \begin{cases} ROP(i)*B & if \ B = \mathbf{l} - 1, \\ ROP(i)*B + 1 & if \ B = \mathbf{l} \ or \ B = \mathbf{l} + 1. \end{cases}$$

- 6. Elements of T(k) are same as ones obtained from the steps 6.1-6.4

- 6.1. Set  $i_0 = 0$  and k = 1;

- 6.1.1 if K=A\*B and B=(I+I) then  $T(k)=MIS(i_0)+I$ ; k=k+1;  $i_0=i_0+1$ ; endif

- <u>6.1.2 for  $i = i_0$ ,  $i_0 + 1$ ,  $i_0 + 2$ , ..., A 1 do</u>

- 6.1.3 z = MIS(i) + BR(0);

- 6.1.4 if  $z \notin K$  then T(k) = z; k = k + 1; else prune z; endif

- 6.1.5 endfor

- 6.2. for j = 1, 2, ..., 1 2 do

- 6.2.1 for  $i = 0, 1, 2, \dots, A 1$  do

- 6.2.2  $z = MIS(i) + BR((j*Q(i))) \mod (I-I);$

- 6.2.3 if  $z \cdot f(k) = z$ ; k = k + 1; else prune z; endif

- 6.2.4 endfor

- 6.2.5 endfor

- 6.3. if (I I) < B then

- 6.3.1 for  $i = 0, 1, 2, \dots, A 1$  do

- 6.3.2 z = MIS(i);

- 6.3.3 if  $z \, \mathcal{L} K$  then T(k) = z; k = k + 1; else prune z; endif

6.3.4 <u>endfor</u>

6.3.5 endif

6.4. if 1 < B then

6.4.1  $i_0 = 0$ ;

6.4.2 if K = A\*B then  $T(k) = MIS(i_0) + 1$ ; k = k + 1;  $i_0 = i_0 + 1$ ; endif

6.4.3 for  $i = i_0$ ,  $i_0 + 1$ ,  $i_0 + 2$ , ..., A - 1 do

6.4.4 z = MIS(i) + 1;

6.4.5 if  $z \notin K$  then T(k) = z; k = k + 1; else prune z; endif

6.4.6 endfor

6.4.7 endif

The total number of pruned indexes is A\*B - K.

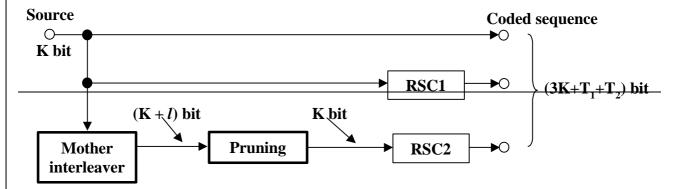

The Turbo code internal interleaver consists of mother interleaver generation and pruning. For arbitrary given block length K, one mother interleaver is selected from the 134 mother interleavers set. The generation scheme of mother interleaver is described in section 4.1.3.2.3.1. After the mother interleaver generation, *l* bits are pruned in order to adjust the mother interleaver to the block length K. The definition of *l* is shown in section 4.1.3.2.3.2.

Figure 5: Overall 8 State PCCC Turbo Coding

#### 4.1.3.2.3.1 Mother interleaver generation

The interleaving consists of three stages. In first stage, the input sequence is written into the rectangular matrix row by row. The second stage is intra row permutation. The third stage is inter row permutation. The three stage permutations are described as follows, the input block length is assumed to be K (320 to 5114 bits).

#### First Stage:

(1) Determine a row number R such that

R=10 (K = 481 to 530 bits; Case 1)

R=20 (K = any other block length except 481 to 530 bits; Case 2)

(2) Determine a column number C such that

Case 1; C = p = 53

Csae 2:

(i) find minimum prime p such that,

0 = <(p+1) K/R,

(ii) if  $(0 = \langle p | K/R)$  then go to (iii),

-else C = p+1.

(iii) if  $(0 = \langle p \mid 1 \mid K/R)$  then  $C = p \mid 1$ ,

-else C = p.

(3) The input sequence of the interleaver is written into the RxC rectangular matrix row by row.

#### **Second Stage:**

## A. If C = p

(A-1) Select a primitive root  $g_{\theta}$  from table 2.

(A 2) Construct the base sequence c(i) for intra row permutation as:

$$c(i) = [g_0 \times c(i-1)] \mod p$$

,  $i = 1, 2, ..., (p-2), c(0) = 1$ .

(A 3) Select the minimum prime integer set  $\{q_i\}$  (j=1,2,...R 1) such that

$$g.c.d\{q_j, p-1\} = 1$$

$q_i > 6$

$q_i > q_{(i-1)}$

where g.c.d. is greatest common divider. And  $q_0 = 1$ .

(A-4) The set  $\{q_i\}$  is permuted to make a new set  $\{p_i\}$  such that

$$p_{P(j)} = q_j, j = 0, 1, \dots R 1,$$

where P(i) is the inter row permutation pattern defined in the third stage.

(A-5) Perform the j-th (j = 0, 1, 2, ..., R-1) intra-row permutation as:

$$c_1(i) = c([i \times p_1] \mod(p-1)), i = 0, 1, 2, ..., (p-2), and c_i(p-1) = 0,$$

where  $c_i(i)$  is the input bit position of i-th output after the permutation of j-th row.

# B. If C = p+1

(B-1) Same as case A-1.

(B-2) Same as case A-2.

(B 3) Same as case A 3.

(B-4) Same as case A-4.

(B-5) Perform the *j*-th (j = 0,1, 2, ..., R-1) intra-row permutation as:

$$c_{j}(i) = c([i \times p_{j}] \mod(p-1)), \quad i = 0, 1, 2, ..., (p-2), c_{j}(p-1) = 0, \text{ and } c_{j}(p) = p,$$

(B 6) If  $(K = C \times R)$  then exchange  $c_{R-1}(p)$  with  $c_{R-1}(0)$ .

where  $c_j(i)$  is the input bit position of i th output after the permutation of j th row.

#### C. If C = p-1

(C-1) Same as case A-1.

(C 2) Same as case A 2.

(C 3) Same as case A 3.

(C-4) Same as case A-4.

(C 5) Perform the j th (j = 0,1, 2, ..., R 1) intra row permutation as:

$$c_i(i) = c([i \times p_i] \mod(p-1)) - 1, \quad i = 0, 1, 2, ..., (p-2),$$

where  $c_i(i)$  is the input bit position of i th output after the permutation of j th row.

# **Third Stage:**

(1) Perform the inter-row permutation based on the following P(j) (j=0,1,...,R-1) patterns, where P(j) is the original row position of the j-th permuted row.

$$P_B$$

: {19, 9, 14, 4, 0, 2, 5, 7, 12, 18, 16, 13, 17, 15, 3, 1, 6, 11, 8, 10} for R=20

$$P_{C}$$

: {9, 8, 7, 6, 5, 4, 3, 2, 1, 0} for  $R=10$

The usage of these patterns is as follows:

Block length K: P(j)

320 to 480-bit: P<sub>A</sub>

481 to 530 bit: P<sub>C</sub>

531 to 2280-bit: PA

2281 to 2480-bit: PB

2481 to 3160 bit: PA

3161 to 3210-bit: PB

3211 to 5114-bit: PA

(2) The output of the mother interleaver is the sequence read out column by column from the permuted R → C matrix.

Table 2: Table of prime  $p\lambda$  and associated primitive root  $\mu$

| <del>p</del> <u>λ</u> | <u>μ</u> <del>g</del> ₀ | <u> </u> | <u>μ<del>g</del></u> ₀ | <del>p</del> <u>λ</u> | <u>μ</u> <del>g</del> ₀ | <u> </u> | <u>μ<del>g</del></u> ₀ | <del>p</del> <u>λ</u> | <u>μ</u> <del>g</del> ₀ |

|-----------------------|-------------------------|----------|------------------------|-----------------------|-------------------------|----------|------------------------|-----------------------|-------------------------|

| 17                    | 3                       | 59       | 2                      | 103                   | 5                       | 157      | 5                      | 211                   | 2                       |

| 19                    | 2                       | 61       | 2                      | 107                   | 2                       | 163      | 2                      | 223                   | 3                       |

| 23                    | 5                       | 67       | 2                      | 109                   | 6                       | 167      | 5                      | 227                   | 2                       |

| 29                    | 2                       | 71       | 7                      | 113                   | 3                       | 173      | 2                      | 229                   | 6                       |

| 31                    | 3                       | 73       | 5                      | 127                   | 3                       | 179      | 2                      | 233                   | 3                       |

| 37                    | 2                       | 79       | 3                      | 131                   | 2                       | 181      | 2                      | 239                   | 7                       |

| 41                    | 6                       | 83       | 2                      | 137                   | 3                       | 191      | 19                     | 241                   | 7                       |

| 43                    | 3                       | 89       | 3                      | 139                   | 2                       | 193      | 5                      | 251                   | 6                       |

| 47                    | 5                       | 97       | 5                      | 149                   | 2                       | 197      | 2                      | 257                   | 3                       |

| 53                    | 2                       | 101      | 2                      | 151                   | 6                       | 199      | 3                      |                       |                         |

# 4.1.3.2.3.2 Definition of number of pruning bits

The output of the mother interleaver is pruned by deleting the *l* bits in order to adjust the mother interleaver to the block length K, where the deleted bits are non existent bits in the input sequence. The pruning bits number *l* is defined as:

$$-l = R \times C - K$$

where R is the row number and C is the column number defined in section 4.1.3.2.3.1.