## TSG-RAN Meeting #19 Birmingham, UK, 11 - 14 March 2003

### Presentation of Specification to TSG or WG

Presentation to: TSG RAN Meeting #19

Document for presentation: TR25.895, Version 1.0.0

Agenda Item: 9.9.9 "Analysis of Higher Chip Rates for UTRA TDD

evolution"

**Presented for:** Information

#### **Abstract of document:**

The document is TR25.895 v1.0.0 "Analysis of higher chip rates for UTRA TDD evolution". It was agreed at RAN1#31 in Tokyo to present this TR to TSG-RAN#19 for information.

#### Changes since last presentation to TSG-RAN Meeting #18:

A version of TR25.895 has not previously been presented to TSG-RAN.

The following sections have been completed in the TR:

- Introduction, scope

- Reference higher chip rate configuration

- Link level results for some HSDPA higher chip rate reference radio bearers

- Backward compatibility feasibility

- Link level simulation assumptions

- System level simulation assumptions

### **Outstanding Issues:**

The following issues are outstanding:

- Link level results for R99 bearers and some HSDPA bearers

- System level simulation results

- Link budget

- Complexity analysis

- Feasibility study in section 6 of TR (other than backward compatibility)

- Recommendations and conclusions

#### **Contentious Issues:**

\_

# 3GPP TR 25.895 V1.0.0 (2003-03)

Technical Report

3rd Generation Partnership Project; Technical Specification Group Radio Access Network; Analysis of higher chip rates for UTRA TDD evolution; (Release 6)

The present document has been developed within the 3<sup>rd</sup> Generation Partnership Project (3GPP TM) and may be further elaborated for the purposes of 3GPP

Keywords <keyword[, keyword]>

#### 3GPP

Postal address

3GPP support office address

650 Route des Lucioles - Sophia Antipolis Valbonne - FRANCE Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16

Internet

http://www.3gpp.org

### **Copyright Notification**

No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

© 2002, 3GPP Organizational Partners (ARIB, CWTS, ETSI, T1, TTA, TTC). All rights reserved.

# Contents

| Forev           | word                                                                       | 5  |

|-----------------|----------------------------------------------------------------------------|----|

| Intro           | duction                                                                    | 5  |

| 1               | Scope                                                                      | 6  |

| 2               | References                                                                 | 6  |

| 3               | Definitions, symbols and abbreviations                                     | 7  |

| 3.1             | Definitions                                                                |    |

| 3.2             | Symbols                                                                    | 7  |

| 3.3             | Abbreviations                                                              | 7  |

| 4               | Reference Higher Chip Rate Configuration                                   | 7  |

| 4.1             | High Level Architecture                                                    |    |

| 4.2             | Radio Aspects                                                              |    |

| 4.3             | Layer 1 Aspects                                                            |    |

| 4.3.1           | Physical channels and mapping of transport channels onto physical channels |    |

| 4.3.2           | Multiplexing and channel coding                                            |    |

| 4.3.3           | Spreading and modulation                                                   | 13 |

| 4.3.4           | Physical Layer Procedures                                                  | 17 |

| 4.3.5           | Physical Layer Measurements                                                |    |

| 4.3.6           | UE Capabilities                                                            |    |

| 4.4             | Protocol aspects                                                           | 18 |

| 5               | Analysis                                                                   | 18 |

| 5.1             | Reference Channel Models                                                   |    |

| 5.2             | Link Level Results                                                         |    |

| 5.3             | System Level Results                                                       |    |

| 5.4             | Link Budget                                                                |    |

| 5.5             | Complexity Analysis                                                        | 21 |

| 5.5.1           | UE Complexity                                                              | 21 |

| 5.5.2           | UTRAN Complexity                                                           | 21 |

| 5.5.3           | Dual mode 3.84Mcps / 7.68Mcps UEs                                          | 21 |

| 6               | Feasibility                                                                | 21 |

| 6.1             | Coexistence with existing UTRA releases                                    | 21 |

| 6.2             | Use in diverse spectrum arrangements and allocations                       | 21 |

| 6.3             | Mobility                                                                   | 22 |

| 6.4             | Application to 3GPP system and services                                    | 22 |

| 6.5             | Backward Compatibility                                                     |    |

| 6.5.1           | Operation of higher chip rate UEs in 3.84Mcps TDD infrastructure           | 22 |

| 6.5.2           | Operation in multiple frequency bands                                      |    |

| 6.5.3           | Operation of 3.84Mcps TDD UEs when higher chip rate UTRAN is deployed      |    |

| 6.5.4           | Servicing of 3.84Mcps TDD UEs under higher chip rate UTRAN                 |    |

| 6.5.4           | Operation of higher chip rate as an auxiliary downlink                     |    |

| 6.6             | Impact on other working groups                                             |    |

| 6.7             | Impact on Specifications                                                   |    |

| 6.8<br>6.9      | Signalling Impact                                                          |    |

| 6.10            | Higher chip rates than 7.68Mcps                                            |    |

|                 |                                                                            |    |

| 7               | Recommendations and Conclusions                                            |    |

|                 | ex A (normative): Link Level Simulation Assumptions                        |    |

| A.1             | Description of Bearer Services                                             |    |

| A.1.1           | <b>√</b> 1                                                                 |    |

| A.1.1.          | 1                                                                          |    |

| A.1.1.<br>A.1.2 |                                                                            |    |

| A.1.2<br>A.2    | Release 5 Type (HSDPA)Applicable Propagation Channels                      |    |

| 13./.           |                                                                            |    |

| A.3       | Deployment Specifics                                                  | 26 |

|-----------|-----------------------------------------------------------------------|----|

| A.4       | Transmitter Assumptions                                               | 26 |

| A.5       | Propagation Channel Simulation Assumptions                            | 27 |

| A.6       | Assumptions on Interference                                           | 27 |

| A.6.1     | Intra-cell                                                            | 27 |

| A.6.1.1   | Downlink                                                              | 27 |

| A.6.1.2   | Uplink                                                                | 27 |

| A.6.2     | Inter-cell                                                            | 28 |

| A.7       | Receiver Assumptions                                                  |    |

| A.8       | Power Control                                                         | 28 |

| A.8.1     | Downlink                                                              | 28 |

| A.8.2     | Uplink                                                                | 28 |

| A.9       | HSDPA Services                                                        | 28 |

| A.10      | Numerical Accuracy                                                    | 29 |

| A.11      | Output Metrics                                                        |    |

| A.11.1    | Speech (12.2kbps) and Circuit Switched Data (384kbps) Bearer Services | 29 |

| A.11.2    | HSDPA Bearer Services                                                 | 29 |

| Annov D   | (normative): System Level Simulation Assumptions                      |    |

|           |                                                                       |    |

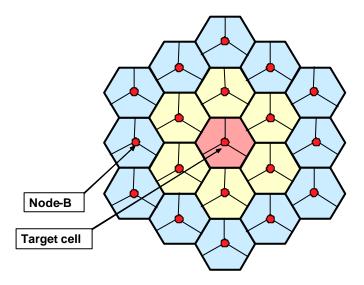

| B.1       | General                                                               |    |

| B.2       | System Level Parameters                                               |    |

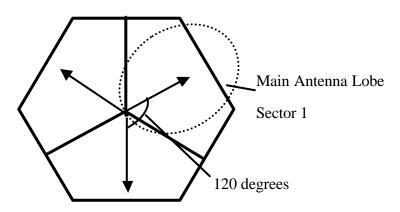

| B.2.1     | Antenna Pattern                                                       |    |

| B.2.2     | Antenna Orientation                                                   |    |

| B.2.3     | Common System Level Assumptions                                       |    |

| B.2.4     | HSDPA specific simulation assumptions                                 |    |

| B.2.4.1   | Chase Combining assumptions                                           |    |

| B.2.4.2   | CQI derivation assumptions                                            |    |

| B.2.4.3   | Size of allocations                                                   |    |

| B.2.4.4   | Scheduling Algorithms                                                 |    |

| B.2.4.4.1 | Proportional Fairness Scheduling                                      |    |

| B.2.4.4.2 | Round Robin Scheduling                                                |    |

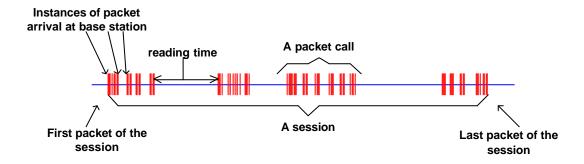

| B.3       | Traffic Models                                                        |    |

| B.3.1     | Release 99 / 4 type bearers                                           |    |

| B.3.2     | Release 5 type bearers                                                |    |

| B.3.2.1   | HTTP Traffic Model Characteristics                                    |    |

| B.3.2.2   | FTP Traffic Model Characteristics                                     |    |

| B.3.3     | Channel Models                                                        |    |

| B.4       | Output Metrics                                                        |    |

| B.4.1     | Release 99 / 4 type bearers                                           |    |

| B.4.1.1   | Definitions                                                           |    |

| B.4.1.1.1 | Satisfied User                                                        |    |

| B.4.1.1.2 | System Load                                                           |    |

| B.4.1.1.3 | Cell Operating Load                                                   |    |

| B.4.1.1.4 | Parameters definitions                                                |    |

| B.4.1.2   | Performance Metrics for Release 99/4 type bearers                     |    |

| B.4.2     | Release 5 type bearers                                                | 39 |

### **Foreword**

This Technical Report has been produced by the 3<sup>rd</sup> Generation Partnership Project (3GPP).

The contents of the present document are subject to continuing work within the TSG and may change following formal TSG approval. Should the TSG modify the contents of the present document, it will be re-released by the TSG with an identifying change of release date and an increase in version number as follows:

Version x.y.z

where:

- x the first digit:

- 1 presented to TSG for information;

- 2 presented to TSG for approval;

- 3 or greater indicates TSG approved document under change control.

- y the second digit is incremented for all changes of substance, i.e. technical enhancements, corrections, updates, etc.

- z the third digit is incremented when editorial only changes have been incorporated in the document.

### Introduction

This technical report presents the results of the 3GPP system Study Item to analyse the use of higher chip rates for UTRA TDD evolution. This study includes an analysis of the feasibility and potential benefits of higher chip rates for UTRA TDD. This study includes a recommendation to RAN Plenary on a potential standardisation work plan and time frame.

Higher chip rate UTRA TDD is studied in the light of the imminent allocation of considerably more spectrum for 3G in bands other than the IMT-2000 band in which systems are currently being deployed, and the demand for higher burst rates and sector throughputs for data traffic in the wide area. Higher chip rate UTRA TDD may be used to support (for instance) personal, multimedia and broadcast services.

Potential benefits of higher chip rate UTRA TDD include system gains from trunking efficiency, link level gains from an ability to better resolve channel paths, the ability to support more accurate location services, higher possible peak bit rates and cell throughputs and an improved ability to reject narrowband interferers.

## 1 Scope

The present document contains results of an analysis of the feasibility and potential benefits of higher chip rate UTRA TDD.

The analysis in this document is based on a reference configuration at the reference chip rate of 7.68Mcps. The comparison of this reference system with current UTRA TDD releases allows conclusions to be drawn as to the potential benefits and feasibility of even higher chip rates for UTRA TDD.

The document presents results of an analysis of the reference configuration using channel models appropriate to a higher chip rate system. Link level and system level results are presented. A link budget shows the coverage that can be expected at a higher chip rate. Aspects of UE and UTRAN complexity are considered.

The feasibility of higher chip rate UTRA TDD systems is considered. This document covers aspects such as coexistence, backward compatibility, use in diverse spectrum arrangements and allocations, mobility, application to 3GPP system and services, antenna systems and impacts on signalling, specifications and RAN working groups.

The study of higher chip rate UTRA TDD is based on the assumption that the higher layer protocol architecture for higher chip rate UTRA TDD is unchanged from 3GPP Release 5. It is assumed that higher chip rate UTRA TDD shall be evolved from 3.84Mcps TDD and that the higher chip rate UTRA TDD carrier may exist without the need for a supporting 3.84Mcps TDD carrier.

### 2 References

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- ?? References are either specific (identified by date of publication, edition number, version number, etc.) or non-specific.

- ?? For a specific reference, subsequent revisions do not apply.

- ?? For a non-specific reference, the latest version applies. In the case of a reference to a 3GPP document (including a GSM document), a non-specific reference implicitly refers to the latest version of that document *in the same Release as the present document.*

```

[1]

3GPP TS 25.301: "Radio Interface Protocol Architecture (Release 5)"

[2]

3GPP TS 25.401: "UTRAN Overall Description (Release 5)"

3GPP TS 25.222: "Multiplexing and channel coding (Release 5)"

[3]

[4]

3GPP TS 25.223: "Spreading and modulation (Release 5)"

3GPP TS 25.221: "Physical channels and mapping of transport channels onto physical channels

[5]

(TDD) (Release 5)"

[6]

3GPP TS 25.224: "Physical Layer Procedures (TDD) (Release 5)"

3GPP TS 25.225: "Physical layer – Measurements (TDD) (Release 5)"

[7]

[8]

3GPP TS 25.102: "UTRA (UE) TDD; Radio transmission and reception (Release 5)"

3GPP TS 25.105: "UTRA (BS) TDD; Radio transmission and reception (Release 5)"

[9]

3GPP TS 25.331: "Radio resource control (RRC) protocol specification (Release 5)"

[10]

```

## 3 Definitions, symbols and abbreviations

### 3.1 Definitions

### 3.2 Symbols

### 3.3 Abbreviations

## 4 Reference Higher Chip Rate Configuration

[Editor's note: This section will describe a reference higher chip rate configuration to enable analysis of feasibility and potential benefits.].

## 4.1 High Level Architecture

The high level protocol architecture (MAC, RLC, RRC and other protocol elements higher than the MAC layer) for the higher chip rate UTRA TDD reference configuration is unchanged from 3GPP Release 5 as described in 25.301 [1].

UTRAN architecture for the higher chip rate reference configuration is unchanged from 3GPP Release 5 as described in 25.401 [2]. The system elements that are considered in the reference configuration are the RNC, Node B and UE.

The layer 1 architecture for the higher chip rate reference configuration is based on an evolution of the 3.84Mcps TDD architecture. The frame structure, power control procedures, HSDPA aspects etc. are based on those of 3.84Mcps TDD.

The higher chip rate UTRA TDD system does not require the support of a 3.84Mcps TDD carrier (a cell may support only the higher chip rate).

The higher chip rate reference configuration uses a chip rate of 7.68Mcps.

## 4.2 Radio Aspects

[Editor's note: covers aspects related to the transmit and receive radios (cf RAN4 specifications) – assumed transmit powers, receive sensitivities and bandwidths].

## 4.3 Layer 1 Aspects

# 4.3.1 Physical channels and mapping of transport channels onto physical channels

### Physical channels

#### Frame Structure

The higher chip rate reference configuration frame has a duration of 10ms and is subdivided into 15 timeslots (as per 3.84Mcps TDD). Each timeslot is of duration  $5120 * T_c$  and can be allocated to either uplink or downlink.

#### **Spreading for Downlink Physical Channels**

Downlink physical channels shall use SF = 32. Multiple parallel physical channels can be used to support higher data rates. These parallel physical channels shall be transmitted using the channelisation codes as defined in section 4.3.3. Operation with a single code with spreading factor 1 is possible for the downlink physical channels.

#### **Spreading for the Uplink Physical Channels**

Spreading for uplink physical channels is identical to that of 3.84 Mcps UTRA TDD mode as stated in section 5.2.1.2 of TS 25.221 [5] with the exception that the range of spreading factor that may be used for uplink physical channels shall range from 32 down to 1.

#### **Burst Types**

Three burst types are defined: all of them comprise two data fields, a midamble and a guard period, the lengths of which are different for the individual burst types. Thus the number of data symbols in a burst depends upon the spreading factor and burst type as defined in Table 1 below:

Spreading Factor (SF) Burst Type 1 Burst Type 2 Burst Type 3 3904 4416 3712 2 2208 1952 1856 4 976 1104 928 8 488 552 464 16 244 276 232 122 138 116

Table 1: number of data symbols (N) for burst type 1, 2, and 3

The support of all three burst types is mandatory for the UE.

#### **Burst Type 1**

Burst type 1 can be used for uplink and downlink. The midamble is of length 1024 chips. The maximum number of midambles for burst type 1 shall be 4, 8, or 16. The burst structure of burst type 1 is shown in Figure 1 below:

| Data symbols<br>1952 chips | Midamble<br>1024 chips | Data symbols<br>1952 chips | GP<br>192<br>CP |

|----------------------------|------------------------|----------------------------|-----------------|

| 4                          | 5120*T <sub>c</sub>    |                            |                 |

Figure 1: Burst structure of burst type 1. GP denotes the guard period and CP denotes chip periods.

#### **Burst Type 2**

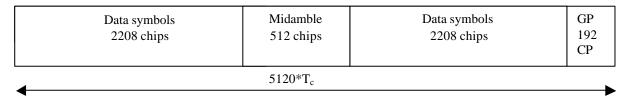

Burst type 2 can be used for uplink and downlink. The midamble is of length 512 chips. The maximum number of midambles for burst type 2 shall be 4 or 8. The burst structure of burst type 2 is shown in Figure 2 below:

Figure 2: Burst structure of burst type 2. GP denotes the guard period and CP denotes chip periods. Burst Type 3

Burst type 3 is used in the uplink only. Due to the longer guard period it is suitable for initial access or access to a new cell after handover. The midamble construction is identical to that of burst type 1. The maximum number of midambles for burst type 3 shall be 4, 8, or 16. The second data field is reduced in length compared to the first data field and the structure of burst type 3 is shown in Figure 3 below:

| Data symbols<br>1952 chips | Midamble<br>1024 chips | Data symbols<br>1760 chips | GP<br>384<br>CP |

|----------------------------|------------------------|----------------------------|-----------------|

| 4                          | 5120*T <sub>c</sub>    |                            |                 |

Figure 3: Burst structure of burst type 3. GP denotes the guard period and CP denotes chip periods.

#### Transmission of TFCI

All burst types 1, 2, and 3 provide the possibility for transmission of TFCI. Transmission of TFCI is identical to that of 3.84 Mcps UTRA TDD mode, see section 5.2.2.4 [5], with the exception that in the uplink the data in the TFCI field are always spread with SF = 32.

#### **Transmission of TPC**

All burst types 1, 2, and 3 provide the possibility for transmission of TPC in the uplink. Transmission of TPC is identical to that of 3.84 Mcps UTRA TDD mode, see section 5.2.2.5 [5], with the exception that the data in the TPC field are always spread with SF = 32.

#### Training sequences for spread bursts

The midamble for burst type 1 or 3 of the reference configuration has a length of Lm=1024, which corresponds to:

$$K' = 8$$

;  $W = 114$ ;  $P = 912$ .

Depending on the possible delay spread, cells are configured to use  $K_{Cell}$  midambles which are generated from the basic midamble codes (which are described below)

- for all k = 1, 2, ..., K; K = 2K' or

- for k = 1, 2, ..., K', only, or

- for odd k = 1,3,5,...,? K', only.

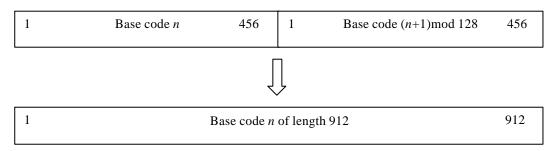

The basic midamble codes of length 912 chips are formed from the concatenation of successive basic midamble codes of length P = 456 (as defined in [5]). I.e. the  $n^{th}$  base code is formed from the concatenation of the  $n^{th}$  and  $m^{th}$  existing base codes of length 456, where  $m = (n+1) \mod 128$ . The concatenation is pictured below in Figure 4.

Figure 4: Basic midamble code construction from existing codes of length 456 for burst types 1 and 3.

The basic midamble codes for burst type 2 of the reference configuration are identical to those of burst type 1/3 at 3.84 Mcps as given in Table A-1 of [5]. The maximum number of midambles for burst type 2 shall be 4 or 8 and the midambles are constructed from the basic midamble codes as described in Section 5.2.3 of [5] with the following parameters: Lm = 512; K' = 8; W = 57; P = 456.

#### Common physical channels

The association between burst type number and physical channels is identical to that of 3.84 Mcps UTRA TDD [5]. All physical channels with the exception of SCH shall be capable of using spreading factor 32. The uplink PRACH uses either spreading factor SF = 32 or SF = 16.

#### **Transmit Diversity for DL Physical Channels**

The transmit diversity schemes that may be applied in the reference configuration are identical to those of 3.84Mcps UTRA TDD (sec. 5.4 of [5]).

#### Beacon characteristics of physical channels

The beacon characteristics of physical channels of the higher chip rate reference configuration shall be identical to those of 3.84Mcps UTRA TDD (sec 5.5 of [5]) with the exception that the beacon channel shall be provided by the physical channel that is allocated to channelisation code  $c_{Q^{?}32}^{(k^{?}1)}$ .

#### **Midamble Transmit Power**

The midamble transmit power of the higher chip rate reference configuration shall be identical to that of 3.84Mcps UTRA TDD (normative part of sec 5.7 of [5]).

#### **Midamble Allocation for Physical Channels**

Midamble allocation for physical channels of the higher chip rate reference configuration shall be identical to that of 3.84Mcps UTRA TDD (sec 5.6 of [5]) with the exception that the association between midambles and channelisation codes is as described below:

#### - Association between Midambles and Channelisation Codes:

The following mapping schemes (defined in Figure 5, Figure 6 and Figure 7) apply for the association between midambles and channelisation codes if no midamble is allocated by higher layers. Secondary channelisation codes are marked with a \*. These associations apply both for UL and DL.

### -- Association for Burst Type 1/3 and $K_{Cell}$ = 16 Midambles

|                                         |                                         |                                         | $\mathbf{m}^{(1)} - \mathbf{c}_8^{(1)}$ | $\mathbf{m}^{(1)} - \mathbf{c}_{16}^{(1)}$   | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                       |

|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|                                         |                                         | $\mathbf{m}^{(1)} - \mathbf{c}_4^{(1)}$ | m – c <sub>8</sub>                      | $\mathbf{m}^{(9)} - \mathbf{c}_{16}^{(2)}$   | $\mathbf{m}^{(9)} - \mathbf{c}_{32}^{(3)}$<br>$\mathbf{m}^{(9)} - \mathbf{c}_{32}^{(4)*}$                                    |

|                                         |                                         | $\mathbf{m}^{*} = \mathbf{c}_4^{*}$     | $\mathbf{m}^{(2)} - \mathbf{c_8}^{(2)}$ | $\mathbf{m}^{(2)} - \mathbf{c}_{16}^{(3)}$   | $\mathbf{m}^{(2)} - \mathbf{c}_{32}^{(5)}$<br>$\mathbf{m}^{(2)} - \mathbf{c}_{32}^{(6)*}$                                    |

|                                         | $\mathbf{m}^{(1)} - \mathbf{c}_2^{(1)}$ |                                         | m – c <sub>8</sub>                      | $\mathbf{m}^{(10)} - \mathbf{c}_{16}^{(4)}$  | $\frac{\mathbf{m}^{(10)} - \mathbf{c}_{32}^{(7)}}{\mathbf{m}^{(10)} - \mathbf{c}_{32}^{(8)*}}$                               |

|                                         | $\mathbf{m} - \mathbf{c}_2$             |                                         | $\mathbf{m}^{(3)} - \mathbf{c_8}^{(3)}$ | $\mathbf{m}^{(3)} - \mathbf{c}_{16}^{(5)}$   | $\begin{array}{c c} \mathbf{m}^{(3)} - \mathbf{c}_{32}^{(9)} \\ \mathbf{m}^{(3)} - \mathbf{c}_{32}^{(10)*} \end{array}$      |

|                                         |                                         | $\mathbf{m}^{(3)} - \mathbf{c}_4^{(2)}$ | III − C <sub>8</sub>                    | $\mathbf{m}^{(11)} - \mathbf{c}_{16}^{(6)}$  | $\frac{\mathbf{m}^{(11)} - \mathbf{c}_{32}^{(11)}}{\mathbf{m}^{(11)} - \mathbf{c}_{32}^{(12)*}}$                             |

|                                         |                                         | III — C4                                | $\mathbf{m}^{(6)} - \mathbf{c_8}^{(4)}$ | $\mathbf{m}^{(6)} - \mathbf{c}_{16}^{(7)}$   | $\mathbf{m}^{(6)} - \mathbf{c}_{32}^{(13)}$<br>$\mathbf{m}^{(6)} - \mathbf{c}_{32}^{(14)*}$                                  |

| $\mathbf{m}^{(1)} - \mathbf{c}_1^{(1)}$ |                                         |                                         | m – c <sub>8</sub>                      | $\mathbf{m}^{(14)} - \mathbf{c}_{16}^{(8)}$  | $\frac{\mathbf{m}^{(14)} - \mathbf{c}_{32}^{(15)}}{\mathbf{m}^{(14)} - \mathbf{c}_{32}^{(16)*}}$                             |

| m - c <sub>1</sub>                      |                                         | $\mathbf{m}^{(5)} - \mathbf{c}_4^{(3)}$ | $\mathbf{m}^{(5)} - \mathbf{c}_8^{(5)}$ | $\mathbf{m}^{(5)} - \mathbf{c}_{16}^{(9)}$   | $ \begin{array}{c c} \mathbf{m}^{(5)} - \mathbf{c}_{32}^{(17)} \\ \mathbf{m}^{(5)} - \mathbf{c}_{32}^{(18)*} \end{array} $   |

|                                         |                                         |                                         | m c <sub>8</sub>                        | $\mathbf{m}^{(13)} - \mathbf{c}_{16}^{(10)}$ |                                                                                                                              |

|                                         |                                         | m c4                                    | $\mathbf{m}^{(4)} - \mathbf{c}_8^{(6)}$ | $\mathbf{m}^{(4)} - \mathbf{c}_{16}^{(11)}$  | $ \begin{array}{c} \mathbf{m}^{(4)} - \mathbf{c}_{32}^{(21)} \\ \mathbf{m}^{(4)} - \mathbf{c}_{32}^{(22)*} \end{array} $     |

|                                         | $\mathbf{m}^{(5)} - \mathbf{c}_2^{(2)}$ |                                         | III                                     | $\mathbf{m}^{(12)} - \mathbf{c}_{16}^{(12)}$ | $\mathbf{m}^{(12)} - \mathbf{c}_{32}^{(23)}$ $\mathbf{m}^{(12)} - \mathbf{c}_{32}^{(24)*}$                                   |

|                                         | <b>m</b> C <sub>2</sub>                 |                                         | $\mathbf{m}^{(7)} - \mathbf{c}_8^{(7)}$ | $\mathbf{m}^{(7)} - \mathbf{c}_{16}^{(13)}$  | $\mathbf{m}^{(7)} - \mathbf{c}_{32}^{(25)}$<br>$\mathbf{m}^{(7)} - \mathbf{c}_{32}^{(26)*}$                                  |

|                                         |                                         | $\mathbf{m}^{(7)} - \mathbf{c}_4^{(4)}$ |                                         | $\mathbf{m}^{(15)} - \mathbf{c}_{16}^{(14)}$ |                                                                                                                              |

|                                         |                                         |                                         | $\mathbf{m}^{(8)} - \mathbf{c}_8^{(8)}$ | $\mathbf{m}^{(8)} - \mathbf{c}_{16}^{(15)}$  | $\mathbf{m}^{(8)} - \mathbf{c}_{32}^{(29)}$ $\mathbf{m}^{(8)} - \mathbf{c}_{32}^{(30)*}$                                     |

|                                         |                                         |                                         |                                         | $\mathbf{m}^{(16)} - \mathbf{c}_{16}^{(16)}$ | $ \begin{array}{c c} \mathbf{m}^{(16)} - \mathbf{c}_{32}^{(31)} \\ \mathbf{m}^{(16)} - \mathbf{c}_{32}^{(32)*} \end{array} $ |

Figure 5 - Association of Midambles to Spreading Codes for Burst Type 1/3 and  $K_{\text{Cell}} = 16\,$

### -- Association for Burst Type 1-3 and $K_{Cell} = 8 \text{ Midambles}$

| $\mathbf{m}^{(1)} - \mathbf{c}_1^{(1)}$ |                                         |                                         |                                         | $\mathbf{m}^{(1)} - \mathbf{c}_{16}^{(1)}$   | $\mathbf{m}^{(1)} - \mathbf{c}_{32}^{(1)}$                                                                                  |                                                                                           |

|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|                                         |                                         |                                         | $\mathbf{m}^{(1)} - \mathbf{c}_8^{(1)}$ | m - c <sub>16</sub>                          | $\mathbf{m}^{(1)} - \mathbf{c}_{32}^{(2)*}$                                                                                 |                                                                                           |

|                                         |                                         | $\mathbf{m}^{(1)} - \mathbf{c}_4^{(1)}$ | III 0,                                  | $\mathbf{m}^{(1)} - \mathbf{c}_{16}^{(2)*}$  | $\mathbf{m}^{(1)} - \mathbf{c}_{32}^{(3)*}$ $\mathbf{m}^{(1)} - \mathbf{c}_{32}^{(4)*}$                                     |                                                                                           |

|                                         |                                         | m - C4                                  | $\mathbf{m}^{(2)} - \mathbf{c_8}^{(2)}$ | $\mathbf{m}^{(2)} - \mathbf{c}_{16}^{(3)}$   | $\mathbf{m}^{(2)} - \mathbf{c}_{32}^{(5)}$ $\mathbf{m}^{(2)} - \mathbf{c}_{32}^{(6)*}$                                      |                                                                                           |

|                                         | $\mathbf{m}^{(1)} - \mathbf{c}_2^{(1)}$ |                                         | III – C8                                | $\mathbf{m}^{(2)} - \mathbf{c}_{16}^{(4)*}$  | $\mathbf{m}^{(2)} - \mathbf{c}_{32}^{(7)*}$ $\mathbf{m}^{(2)} - \mathbf{c}_{32}^{(8)*}$                                     |                                                                                           |

|                                         | m - c <sub>2</sub>                      |                                         | $\mathbf{m}^{(3)} - \mathbf{c_8}^{(3)}$ | $\mathbf{m}^{(3)} - \mathbf{c}_{16}^{(5)}$   | $\begin{array}{c c} \mathbf{m}^{(3)} - \mathbf{c}_{32}^{(9)} \\ \mathbf{m}^{(3)} - \mathbf{c}_{32}^{(10)*} \end{array}$     |                                                                                           |

|                                         |                                         | $\mathbf{m}^{(3)} - \mathbf{c}_4^{(2)}$ | C <sub>0</sub>                          | ${\bf m}^{(3)} - {\bf c}$                    | $\mathbf{m}^{(3)} - \mathbf{c}_{16}^{(6)*}$                                                                                 | $\mathbf{m}^{(3)} - \mathbf{c}_{32}^{(11)*}$ $\mathbf{m}^{(3)} - \mathbf{c}_{32}^{(12)*}$ |

|                                         |                                         | <b>III</b> C4                           | $\mathbf{m}^{(6)} - \mathbf{c_8}^{(4)}$ | $\mathbf{m}^{(6)} - \mathbf{c}_{16}^{(7)}$   | $\mathbf{m}^{(6)} - \mathbf{c}_{32}^{(13)}$ $\mathbf{m}^{(6)} - \mathbf{c}_{32}^{(14)*}$                                    |                                                                                           |

|                                         | $\mathbf{m}^{(5)} - \mathbf{c}_2^{(2)}$ |                                         | III                                     | $\mathbf{m}^{(6)} - \mathbf{c}_{16}^{(8)*}$  | $ \begin{array}{c c} \mathbf{m}^{(6)} - \mathbf{c}_{32}^{(15)*} \\ \mathbf{m}^{(6)} - \mathbf{c}_{32}^{(16)*} \end{array} $ |                                                                                           |

|                                         |                                         | $\mathbf{m}^{(5)} - \mathbf{c}_4^{(3)}$ | $\mathbf{m}^{(5)} - \mathbf{c_8}^{(5)}$ | $\mathbf{m}^{(5)} - \mathbf{c}_{16}^{(9)}$   | $\mathbf{m}^{(5)} - \mathbf{c}_{32}^{(17)}$ $\mathbf{m}^{(5)} - \mathbf{c}_{32}^{(18)*}$                                    |                                                                                           |

|                                         |                                         |                                         | m – c <sub>8</sub>                      | $\mathbf{m}^{(5)} - \mathbf{c}_{16}^{(10)*}$ | $\mathbf{m}^{(5)} - \mathbf{c}_{32}^{(19)*}$<br>$\mathbf{m}^{(5)} - \mathbf{c}_{32}^{(20)*}$                                |                                                                                           |

|                                         | $\mathbf{m}^{(4)} - \mathbf{c_8}^{(6)}$ | $\mathbf{m}^{(4)} - \mathbf{c}_{16}^{(11)}$  | $\begin{array}{c} \mathbf{m}^{(4)} - \mathbf{c}_{32}^{(21)} \\ \mathbf{m}^{(4)} - \mathbf{c}_{32}^{(22)*} \\ \mathbf{m}^{(4)} - \mathbf{c}_{32}^{(23)*} \\ \mathbf{m}^{(4)} - \mathbf{c}_{32}^{(24)*} \end{array}$ |

|-----------------------------------------|-----------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | III – C8                                | $\mathbf{m}^{(4)} - \mathbf{c}_{16}^{(12)*}$ | $\mathbf{m}^{(4)} - \mathbf{c}_{32}^{(23)*}$ $\mathbf{m}^{(4)} - \mathbf{c}_{32}^{(24)*}$                                                                                                                          |

|                                         | $\mathbf{m}^{(7)} - \mathbf{c_8}^{(7)}$ | $\mathbf{m}^{(7)} - \mathbf{c}_{16}^{(13)}$  | $\mathbf{m}^{(7)} - \mathbf{c}_{32}^{(25)}$<br>$\mathbf{m}^{(7)} - \mathbf{c}_{32}^{(26)*}$                                                                                                                        |

| $\mathbf{m}^{(7)} - \mathbf{c}_4^{(4)}$ | m - c <sub>8</sub>                      | $\mathbf{m}^{(7)} - \mathbf{c}_{16}^{(14)*}$ | $ \frac{\mathbf{m}^{(7)} - \mathbf{c}_{32}^{(27)^*}}{\mathbf{m}^{(7)} - \mathbf{c}_{32}^{(28)^*}} $                                                                                                                |

| m – <b>c</b> 4                          | $\mathbf{m}^{(8)} - \mathbf{c_8}^{(8)}$ | $\mathbf{m}^{(8)} - \mathbf{c}_{16}^{(15)}$  | $\mathbf{m}^{(8)} - \mathbf{c}_{32}^{(29)}$<br>$\mathbf{m}^{(8)} - \mathbf{c}_{32}^{(30)*}$                                                                                                                        |

|                                         | III – C8                                | $\mathbf{m}^{(8)} - \mathbf{c}_{16}^{(16)*}$ | $\mathbf{m}^{(8)} - \mathbf{c}_{32}^{(31)*}$ $\mathbf{m}^{(8)} - \mathbf{c}_{32}^{(32)*}$                                                                                                                          |

Figure 6 - Association of Midambles to Spreading Codes for Burst Type 1-3 and  $K_{\text{Cell}} = 8$

### -- Association for Burst Type 1-3 and $K_{Cell}$ = 4 Midambles

|                                         |                                         |                                         | $\mathbf{m}^{(1)} - \mathbf{c}_8^{(1)}$  | $\mathbf{m}^{(1)} - \mathbf{c}_{16}^{(1)}$   | $\mathbf{m}^{(1)} - \mathbf{c}_{32}^{(1)}$<br>$\mathbf{m}^{(1)} - \mathbf{c}_{32}^{(2)*}$                                                                                          |

|-----------------------------------------|-----------------------------------------|-----------------------------------------|------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         |                                         | $\mathbf{m}^{(1)} - \mathbf{c}_4^{(1)}$ | <b>m</b>                                 | $\mathbf{m}^{(1)} - \mathbf{c}_{16}^{(2)*}$  | $\begin{array}{c c} \mathbf{m}^{(1)} - \mathbf{c}_{32}^{(3)*} \\ \hline \mathbf{m}^{(1)} - \mathbf{c}_{32}^{(4)*} \\ \hline \mathbf{m}^{(1)} - \mathbf{c}_{32}^{(5)*} \end{array}$ |

|                                         |                                         | m <sup></sup> - c <sub>4</sub>          | $\mathbf{m}^{(1)} - \mathbf{c_8}^{(2)*}$ | $\mathbf{m}^{(1)} - \mathbf{c}_{16}^{(3)*}$  | $\mathbf{m}^{(1)} - \mathbf{c}_{32}^{(6)^*}$                                                                                                                                       |

|                                         | $\mathbf{m}^{(1)} - \mathbf{c}_2^{(1)}$ |                                         | m - c <sub>8</sub>                       | $\mathbf{m}^{(1)} - \mathbf{c}_{16}^{(4)*}$  | $\mathbf{m}^{(1)} - \mathbf{c}_{32}^{(7)*}$<br>$\mathbf{m}^{(1)} - \mathbf{c}_{22}^{(8)*}$                                                                                         |

|                                         | m - c <sub>2</sub>                      |                                         | $\mathbf{m}^{(3)} - \mathbf{c}_8^{(3)}$  | $\mathbf{m}^{(3)} - \mathbf{c}_{16}^{(5)}$   |                                                                                                                                                                                    |

|                                         |                                         | $\mathbf{m}^{(3)} - \mathbf{c}_4^{(2)}$ | III — C8                                 | $\mathbf{m}^{(3)} - \mathbf{c}_{16}^{(6)*}$  | $\mathbf{m}^{(3)} - \mathbf{c}_{32}^{(11)*}$<br>$\mathbf{m}^{(3)} - \mathbf{c}_{32}^{(12)*}$                                                                                       |

|                                         |                                         | <b>III</b> C4                           | $\mathbf{m}^{(3)} - \mathbf{c_8}^{(4)*}$ | $\mathbf{m}^{(3)} - \mathbf{c}_{16}^{(7)*}$  | $\mathbf{m}^{(3)} - \mathbf{c}_{32}^{(13)*}$<br>$\mathbf{m}^{(3)} - \mathbf{c}_{32}^{(14)*}$                                                                                       |

| $\mathbf{m}^{(1)} - \mathbf{c}_1^{(1)}$ |                                         |                                         | III                                      | $\mathbf{m}^{(3)} - \mathbf{c}_{16}^{(8)*}$  | $\mathbf{m}^{(3)} - \mathbf{c}_{32}^{(15)*}$<br>$\mathbf{m}^{(3)} - \mathbf{c}_{32}^{(16)*}$                                                                                       |

| m c <sub>1</sub>                        |                                         |                                         | $\mathbf{m}^{(5)} - \mathbf{c}_8^{(5)}$  | $\mathbf{m}^{(5)} - \mathbf{c}_{16}^{(9)}$   | $\mathbf{m}^{(5)} - \mathbf{c}_{32}^{(17)}$ $\mathbf{m}^{(5)} - \mathbf{c}_{32}^{(18)*}$                                                                                           |

|                                         |                                         | $\mathbf{m}^{(5)} - \mathbf{c}_4^{(3)}$ | C <sub>8</sub>                           | $\mathbf{m}^{(5)} - \mathbf{c}_{16}^{(10)*}$ | $\mathbf{m}^{(5)} - \mathbf{c}_{32}^{(19)*}$<br>$\mathbf{m}^{(5)} - \mathbf{c}_{32}^{(20)*}$                                                                                       |

|                                         |                                         | <b>M</b> C4                             | $\mathbf{m}^{(5)} - \mathbf{c}_8^{(6)*}$ | $\mathbf{m}^{(5)} - \mathbf{c}_{16}^{(11)*}$ | $\mathbf{m}^{(5)} - \mathbf{c}_{32}^{(21)*}$<br>$\mathbf{m}^{(5)} - \mathbf{c}_{32}^{(22)*}$                                                                                       |

|                                         | $\mathbf{m}^{(5)} - \mathbf{c}_2^{(2)}$ |                                         |                                          | $\mathbf{m}^{(5)} - \mathbf{c}_{16}^{(12)*}$ | $\mathbf{m}^{(5)} - \mathbf{c}_{32}^{(23)*}$<br>$\mathbf{m}^{(5)} - \mathbf{c}_{32}^{(24)*}$                                                                                       |

|                                         |                                         |                                         | $\mathbf{m}^{(7)} - \mathbf{c}_8^{(7)}$  | $\mathbf{m}^{(7)} - \mathbf{c}_{16}^{(13)}$  | $\mathbf{m}^{(7)} - \mathbf{c}_{32}^{(25)}$<br>$\mathbf{m}^{(7)} - \mathbf{c}_{32}^{(26)*}$                                                                                        |

|                                         |                                         | $\mathbf{m}^{(7)} - \mathbf{c}_4^{(4)}$ |                                          | $\mathbf{m}^{(7)} - \mathbf{c}_{16}^{(14)*}$ | $\mathbf{m}^{(7)} - \mathbf{c}_{32}^{(27)*}$ $\mathbf{m}^{(7)} - \mathbf{c}_{32}^{(28)*}$                                                                                          |

|                                         |                                         | ,                                       | $\mathbf{m}^{(7)} - \mathbf{c_8}^{(8)*}$ | $\mathbf{m}^{(7)} - \mathbf{c}_{16}^{(15)*}$ | $\mathbf{m}^{(7)} - \mathbf{c}_{32}^{(29)*}$<br>$\mathbf{m}^{(7)} - \mathbf{c}_{32}^{(30)*}$                                                                                       |

|                                         |                                         |                                         | Ů                                        | $\mathbf{m}^{(7)} - \mathbf{c}_{16}^{(16)*}$ | $\mathbf{m}^{(7)} - \mathbf{c}_{32}^{(31)*} \\ \mathbf{m}^{(7)} - \mathbf{c}_{32}^{(32)*}$                                                                                         |

Figure 7 - Association of Midambles to Spreading Codes for Burst Type 1-3 and  $K_{\text{Cell}} = 4$

### Mapping of transport channels to physical channels

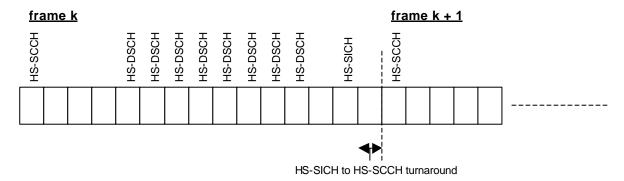

The mapping of transport channels to physical channels is identical to that of 3.84Mcps TDD of section 7 of [5] with the exception that a maximum of (M=8) HS-SCCH may be associated with an HS-DSCH for one UE.

### 4.3.2 Multiplexing and channel coding

The higher chip rate reference configuration shall apply the 3.84Mcps TDD method of multiplexing and channel coding as defined in 25.222 [3] with the following exceptions :

The channelisation code-set information field of the HS-SCCH shall be 10 bits  $(x_{ccs,1},...x_{ccs,10})$  (cf section 4.6 of 25.222 [3]).  $x_{ccs,1},...x_{ccs,5}$  define the start code of the allocation,  $x_{ccs,6},...x_{ccs,10}$  define the stop code of the allocation. If the signaled start code of the allocation is 32 and the signaled stop code is 1, a spreading factor SF=1 shall be used for the HS-PDSCH resources.

Note that the transport block size information for HS-SCCH for the higher chip rate reference configuration shall be coded on 9 bits as per 3.84Mcps TDD. It may be assumed that a mapping of transport block size information to actual transport block size is available that does not significantly impact performance.

### 4.3.3 Spreading and modulation

The higher chip rate reference configuration shall apply the 3.84Mcps TDD method of spreading and modulation as defined in TS 25.223 [4] with the following exceptions:

#### General

The basic modulation parameters of the 7.68 Mcps UTRA TDD reference system are given in Table 2:

Chip rate 7.68 Mcps

Data modulation QPSK / 16 QAM (HS-PDSCH only)

Spreading characteristics Orthogonal Q chips / symbol, Where  $O = 2^p$ , O <= p <= 5

Table 2 - Basic modulation parameters of reference configuration

#### **Data Modulation**

The data modulation is identical to that of 3.84 Mcps UTRA TDD mode (cf section 5 of 25.223 [4]). The number of symbols per data field is adapted to the burst formats defined in section 4.3.1.

#### **Spreading Modulation**

The spreading modulation is identical to that of 3.84 Mcps UTRA TDD mode (cf section 7 of 25.223 [4]) with the exception that the real valued channelisation codes are of length  $Q_k$ ? {1,2,4,8,16,32}. The channelisation codes are Orthogonal Variable Spreading Factor (OVSF) codes and are generated as described for 3.84 Mcps UTRA TDD mode.

Associated with each channelisation code is a multiplier taking values from the set {  $e^{j?/2?p_k}$  }, where  $p_k$  is a permutation of the integer set  $\{0,...,Q_k-1\}$  and  $Q_k$  is the spreading factor. The values of the multiplier for  $Q_k = \{1,2,4,8,16\}$  are identical to those of 3.84 Mcps UTRA TDD mode. For  $Q_k = 32$  the multiplier values are given in Table 3:

Table 3 - multiplier values for  $Q_k = 32$

| K                | 1  | 2  | 3  | 4 | 5  | 6  | 7 | 8 | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|------------------|----|----|----|---|----|----|---|---|----|----|----|----|----|----|----|----|

| $W_{Q?32}^{(k)}$ | -i | -1 | -1 | 1 | -1 | -i | i | 1 | -1 | 1  | 1  | -i | i  | -1 | i  | -i |

| ı |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | i  |

|---|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| ı | V   | 17 | 18 | 19 | 20 | 21 | 22 | 22 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 |

| ı | IZ. | 1/ | 10 | 17 | 20 | 21 | 22 | 23 | 24 | 23 | 20 | 21 | 20 | 23 | 30 | 31 | 32 |

|   |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

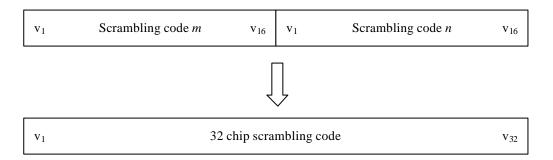

The scrambling codes for the 7.68 Mcps UTRA TDD reference system shall be of length 32 chips and are formed by concatenation of the existing length 16 chip scrambling codes described in Annex A of TS 25.223 [4]. The concatenation of existing scrambling codes m and n is shown in Figure 8 where m, n?  $\{0,...,127\}$  and m? n:

Figure 8: Concatenation of length 16 chip scrambling codes.

The mapping scheme for Cell Parameters and constituent scrambling codes for the 7.68 Mcps UTRA TDD reference system is shown in Table 4. The cycling of cell parameters with system frame numbering is identical to that of the 3.84 Mcps UTRA TDD mode as described in Section 8.3 (Table 7) of TS 25.233 [4].

Table 4: Mapping scheme for Cell Parameters and TS 25.223 constituent scrambling codes.

| Cell      | TS 25.223  | TS 25.223  |

|-----------|------------|------------|

| Parameter | scrambling | scrambling |

|           | code m     | code n     |

| 0         | 0          | 2          |

| 1         | 1          | 3          |

| 2         | 2          | 4          |

| 3         | 3          | 5          |

|           |            |            |

|           |            |            |

|           |            |            |

|           |            |            |

| 124       | 124        | 126        |

| 125       | 125        | 127        |

| 126       | 126        | 0          |

| 127       | 127        | 1          |

When different physical channels are combined in the uplink the weight factors  $?_i$  of Table 5 are applied depending on the spreading factor SF of the corresponding DPCH.

Table 5 - weight factors for reference configuration

| SF of DPCH <sub>i</sub> | <b>?</b> <sub>i</sub> |

|-------------------------|-----------------------|

| 32                      | $\sqrt{2}/8$          |

| 16                      | 1/4                   |

| 8                       | $\sqrt{2}/4$          |

| 4 | 1/2          |

|---|--------------|

| 2 | $\sqrt{2}/2$ |

| 1 | 1            |

#### **Synchronisation codes**

#### **Code Generation**

The synchronisation codes shall be constructed in the same manner as defined in sub-clause 8.1 of [4]. For the 7.68Mcps reference configuration repetition encoding shall be applied to both the primary and secondary synchronization codes. In this instance each element of the code is repeated twice.

Using the notation of sub-clause 8.1 of [4], the primary synchronization code is defined as

$$C_p$$

?  $\langle y(0), y(0), y(1), y(1), \square$  ,  $y(255), y(255) \rangle$

Similarly, the i<sup>th</sup> secondary SCH code word,  $C_i$ , i = 0, 1, 3, 4, 5, 6, 8, 10, 12, 13, 14, 15 is defined as

$$C_{i}? 1? j?? \langle h_{m} 10?? z 10?, h_{m} 10?? z 10?, h_{m} 11?? z 11?, h_{m} 11?? z 11? \Box, h_{m} 1255?? z 1255?, h_{m} 1255?? z 1255?$$

where m? 16? i? and the leftmost chip in the sequence corresponds to the chip transmitted first in time. The length of the synchronization codes in the SCH is 512.

#### **Code Allocation**

Code allocation is identical to sub-clause 8.2 of [4] with the following exceptions to 8.2.1 and 8.2.2:

#### **Code Allocation for Case 1**

There are 32 code groups 0,1,...,31, define u?  $u_0, u_1, u_2, u_3, u_4$ ? as the binary representation of the code group number. The radio frame is denoted by

$$f ? ?0$$

Frame 1

?1 Frame 2

and denote  $C_r$  as a Boolean variable, where

$$C_r$$

? ?  $?$  3.84Mcps 7.68Mcps

Define the following generator matrix

with rows  $g_0^{\eta,\gamma}, g_1^{\eta,\gamma}, g_2^{\eta,\gamma}, g_3^{\eta,\gamma}, g_4^{\eta,\gamma}$  , and the binary codeword a as

$$a ? \ dG^{(1)} ? z \ mod 2$$

where a?  $a_0 \square$ ,  $a_5 ?$ , d?  $c_r \square$ ,  $a_0 \square$ ,  $a_1 \square$  and  $a_1 \square$  and  $a_2 \square$  and  $a_2 \square$  and  $a_3 \square$  and  $a_4 \square$  and  $a_5 \square$  . Map the elements of the codeword  $a_5 \square$  pairwise to the set of integers  $a_5 \square$  using the expression

$$s_k$$

?  $2a_{2k?1}$  ?  $a_{2k}$  ;  $k$  ? 0,1,2

The sequence s?  ${}^{?}s_0, s_1, s_2$ ? has an associated complex sequence b?  ${}^{?}j^{s_0}, j^{s_1}, j^{s_2}$ . The code construction is defined by the component wise product:

$$C_s$$

?  $bC$

The code set permutation is given in Table 6 below. When  $C_r$ ? 0, the codeword produced by the generator matrix matches the sequences defined in sub-clause 8.2.1 of [4].

| $\mathcal{I}_{u_4,u_3,u_2}$ ? | Code Group | Code Set Permutation, $C$ |

|-------------------------------|------------|---------------------------|

| 000                           | 0? 3       | $c_{1}c_{3}c_{5}$         |

| 001                           | 4? 7       | $c_{1}c_{3}c_{5}$         |

| 010                           | 8? 11      | $c_{1}c_{5}c_{3}$         |

| 011                           | 12? 15     | $c_{3}c_{5}c_{1}$         |

| 100                           | 16? 19     | $c_{10}c_{13}c_{14}$      |

| 101                           | 20? 23     | $c_{10}c_{13}c_{14}$      |

| 110                           | 24? 27     | $c_{10}c_{14}c_{13}$      |

| 111                           | 28? 31     | $c_{13}c_{14}c_{10}$      |

Table 6- code set permutations for case 1

#### **Code Allocation for Case 2**

There are 32 code groups 0,1,...,31, define u?  $u_0,u_1,u_2,u_3,u_4$ ? as the binary representation of the code group number, where  $u_0$  is the LSB. The radio frame is denoted by

Denote  $C_r$  as a Boolean variable, where

and

$$TS ? \stackrel{?0}{?} \quad \text{slot } k$$

Define the following generator matrix

with rows labelled  $g_0^{?2?}, g_1^{?2?}, g_2^{?2?}, g_3^{?2?}, g_4^{?2?}$  and the binary codeword a as

$$a ? dG^{(2)} ? z \mod 2$$

where a?  $?a_0, \square$ ,  $a_5$ ?, d?  $?C_r, TS$ , f,  $u_0$ ,  $u_1$ ?, and z?  $u_2$   $u_1$ ?  $1? \mod 2$ ?  $g_4$ ??. Map the elements of the codeword a pairwise to the set of integers ?0,1,2,3? using the expression

$$s_k$$

?  $2a_{2k?1}$  ?  $a_{2k}$  ;  $k$  ?  $0,1,2$

The sequence s?  $?s_0, s_1, s_2$ ? has an associated complex sequence b?  $?j^{s_0}, j^{s_1}, j^{s_2}$ ?. The code construction is defined by the component wise product:

$$C_s$$

?  $bC$

The code set permutation is defined in Table 7 below. When  $C_r$ ? 0 the codeword produced by the generator matrix matches the sequences defined in sub-clause 8.2.2 of [4].

**Table 7 - code set permutations for case 2**

| $u_4, u_3, u_2, u_1$ ? | Code Group | Code Set Permutation, $C$ |

|------------------------|------------|---------------------------|

| 0000                   | 0? 1       | $c_1 c_3 c_5$             |

| 0001                   | 2? 3       | $c_{1}c_{3}c_{5}$         |

| 0010                   | 4? 5       | $c_{1}c_{5}c_{3}$         |

| 0011                   | 6? 7       | $c_{3}c_{5}c_{1}$         |

| 0100                   | 8? 9       | $c_{10}c_{13}c_{14}$      |

| 0101                   | 10? 11     | $c_{10}c_{13}c_{14}$      |

| 0110                   | 12? 13     | $c_{10}c_{14}c_{13}$      |

| 0111                   | 14? 15     | $c_{13}c_{14}c_{10}$      |

| 1000                   | 16? 17     | $c_{0}c_{6}c_{12}$        |

| 1001                   | 18? 19     | $c_{0}c_{6}c_{12}$        |

| 1010                   | 20? 21     | $c_{0}c_{12}c_{6}$        |

| 1011                   | 22? 23     | $c_{6}c_{12}c_{0}$        |

| 1100                   | 24? 25     | $c_4^{}c_8^{}c_{15}^{}$   |

| 1101                   | 26? 27     | $c_4^{}c_8^{}c_{15}^{}$   |

| 1110                   | 28? 29     | $c_{4}c_{15}c_{8}$        |

| 1111                   | 30? 31     | $c_{8}c_{15}c_{4}$        |

## 4.3.4 Physical Layer Procedures

The higher chip rate reference configuration shall apply the 3.84Mcps TDD physical layer procedures as defined in 25.224 [6] with the following exceptions:

#### **Timing Advance**

The required timing advance shall be represented as a 6-bit number (0-63) 'UL Timing Advance'  $TA_{ul}$ , being the multiplier of 4?  $C_r$ ? 1? chips which is nearest to the required timing advance, where

On receipt of  $TA_{ul}$  the UE shall adjust the timing of its transmissions accordingly in steps of 4?  $C_r$ ? 1? chips.

#### **Cell Search Procedure**

A higher chip rate enabled UE can be reconfigured to operate at 3.84Mcps and 7.68Mcps.

#### Step 2: Cell Chip Rate, Code Group Identification and Slot synchronization

During the second step of the cell search procedure, the UE shall use the SCH's secondary synchronization codes to simultaneously identify both cell chip rate and 1 out of 32 code groups for the cell found in the first step. Since this information is solely contained in the modulation sequence, the same method of sequence identification employed at

3.84Mcps can be reused at 7.68Mcps. Before proceeding to the third step of the cell search procedure, there shall be a reconfiguration of the UE transmitter and receiver to reflect the signaled cell chip rate.

### 4.3.5 Physical Layer Measurements

The physical layer measurements defined for the reference configuration are identical to those defined in [7] for 3.84Mcps TDD with the following exceptions :

#### SFN-SFN Observed time difference

The SFN-SFN observed time difference is defined identically to [7] where for 7.68Mcps:

SFN-SFN observed time difference = OFF? 76800 ?  $T_m$  in chips for 7.68Mcps TDD where:

$T_m$  is in the range [0,1,...,76799 chips for 7.68 Mcps TDD]?

#### SFN-CFN observed time difference

$T_m$  is in the range 0,1,...,76799 chips for 7.68 Mcps TDD?

### 4.3.6 UE Capabilities

The reference configuration shall assume that UEs are not restricted in terms of their UE capabilities. The reference configuration shall assume that a form of multi-user detector used at 3.84Mcps is modified to operate at the higher chip rate

### 4.4 Protocol aspects

The reference configuration assumes that there are no protocol changes from 3.84Mcps TDD. It is assumed that higher layer signalling is extended to cover the higher chip rate.

## 5 Analysis

[Editor's note: This section will provide results on the performance and complexity of the reference higher chip rate configuration described in section 4].

### 5.1 Reference Channel Models

[Editor's note: simulations in clause 5 are based on the reference channel models in this subclause. The channel models in this subclause allow for a fair evaluation of higher chip rate UTRA TDD relative to current releases]

### 5.2 Link Level Results

## 5.2.1 Release 99/4 type bearers

[Editor's note: to be included].

## 5.2.2 Release 5 type (HSDPA) bearers

[Editor's note: link level results for some 7.68Mcps HSDPA reference channels in 2 channel types are included. Other channel types and results for 3.84Mcps are required].

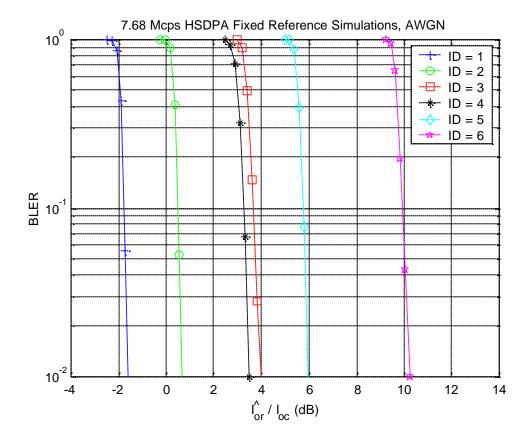

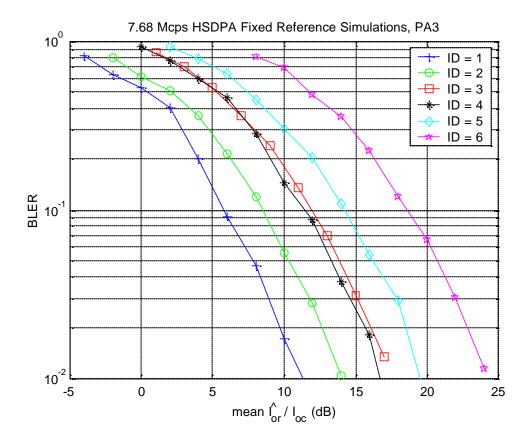

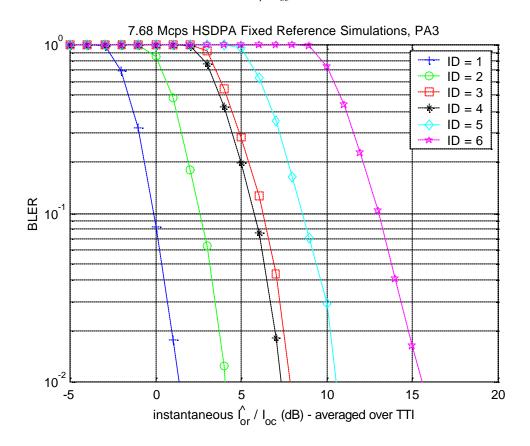

Link level results for 7.68Mcps release 5 type HSDPA bearers are provided in the figures of this subclause according to table 8. Note that the "ID" in these figures refers to the fixed reference channel ID of Table A.1.

**Table 8 - List of Link Level Results Figures**

| figure | channel | mean / instantaneous | chip rate |

|--------|---------|----------------------|-----------|

| 9      | AWGN    | mean                 | 7.68      |

| 10     | PA3     | mean                 | 7.68      |

| 11     | PA3     | instantaneous        | 7.68      |

| [etc.] | [etc.]  | [etc.]               | [etc.]    |

Figure 9 - Link level results for 7.68Mcps HSDPA fixed reference channel simulations in AWGN (mean  $\hat{I}_{or}/I_{oc}$  )

Figure 10 – Link level results for 7.68Mcps HSDPA fixed reference channel simulations in channel PA3 (mean  $\hat{I}_{or}/$

Figure~11-Link~level~results~for~7.68 Mcps~HSDPA~fixed~reference~channel~simulations~in~channel~PA3

(instantaneous

$$\hat{I}_{or} / I_{oc}$$

averaged over a TTI)

## 5.3 System Level Results

[Editor's note: This section provides results on cell throughput, outage, number of users supported for varying radio bearer configurations etc.]

### 5.4 Link Budget

[Editor's note: This section examines the link budget of the reference configuration. Coverage can be derived from the link budget performance].

## 5.5 Complexity Analysis

[Editor's note: the complexity analyses in sections 5.5.1, 5.5.2 and 5.5.3 shall account for the complexity impact of a higher chip rate UTRA TDD being required to decode up to M=8 HS-SCCH compared to the M=4 HS-SCCH that must be decoded by a 3.84Mcps TDD UE].

### 5.5.1 UE Complexity

[Editor's note: Analysis of higher chip rate UTRA TDD UE complexity, comparison relative to 3.84Mcps TDD Release 5].

### 5.5.2 UTRAN Complexity

[Editor's note: Analysis of higher chip rate UTRA TDD UTRAN complexity, comparison relative to 3.84Mcps TDD Release 5: Node B and RNC].

## 5.5.3 Dual mode 3.84Mcps / 7.68Mcps UEs

[Editor's note: Analysis of feasibility from a complexity and performance perspective of dual mode TDD UEs in order to allow for roaming and backwards compatibility (a dual mode TDD UE is understood in this context to implement both 3.84Mcps TDD and 7.68Mcps TDD)].

## 6 Feasibility

## 6.1 Coexistence with existing UTRA releases

[Editor's note: Discusses aspects of the coexistence of high chip rate UTRA TDD with 3.84Mcps TDD and FDD that are within the scope of 3GPP. Coexistence will be considered in diverse spectrum arrangements and allocations such as future spectrum allocations. Aspects of coexistence between higher chip rate TDD and FDD will be compared to Release 99 coexistence].

## 6.2 Use in diverse spectrum arrangements and allocations

[Editor's note: Discusses in which spectrum arrangements and allocations UTRA TDD may be feasible].

## 6.3 Mobility

[Editor's note: feasibility of mobility between higher chip rate UTRA TDD, 3.84Mcps TDD, FDD and GSM. Mobility in RRC connected mode states and idle mode shall be considered. Mobility aspects to and from higher chip rate UTRA TDD shall be considered: for example in the case of handover, feasibility of handover from higher chip rate UTRA TDD to higher chip rate UTRA TDD, 3.84Mcps TDD, FDD and GSM as well as feasibility of handover to higher chip rate UTRA TDD from higher chip rate UTRA TDD, 3.84Mcps TDD, FDD and GSM are considered].

## 6.4 Application to 3GPP system and services

[Editor's note: feasibility of supporting personal, multimedia, broadcast etc. services on higher chip rate UTRA TDD].

## 6.5 Backward Compatibility

### 6.5.1 Operation of higher chip rate UEs in 3.84Mcps TDD infrastructure

It is clear that a UE that can only operate at the higher chip rate will not get service from a 3.84Mcps UTRAN. This situation is analogous to the case where DCS1800 only UEs do not get service from a GSM900 network.

Due to the similarity in the coding of the SCH, a dual mode (higher chip rate / 3.84Mcps TDD) UE is able to identify the chip rate and code group for a cell no matter whether the cell operates at 3.84Mcps or the higher chip rate. If, from the modulation of the SCH, the dual mode UE identifies that the cell operates at 3.84Mcps, it can reconfigure itself to operate at 3.84Mcps.

### 6.5.2 Operation in multiple frequency bands

In the case that higher chip rate TDD is implemented solely in one frequency band and 3.84Mcps TDD is implemented solely in another frequency band, there are no backwards compatibility issues: 3.84Mcps UEs are serviced in one band, higher chip rate UEs in the other band, dual mode UEs may be serviced in either band.

## 6.5.3 Operation of 3.84Mcps TDD UEs when higher chip rate UTRAN is deployed

When 3.84Mcps TDD carriers and higher chip rate TDD carriers are both deployed in the same band, 3.84Mcps UEs will not attempt to camp on to higher chip rate carriers since they:

- 1) are unlikely to correctly decode the code group for the higher chip rate cell

- 2) will be unable to correctly read system information and will thus reject the higher chip rate cell

These 3.84Mcps TDD UEs will then be able to camp on 3.84Mcps carriers in the same band.

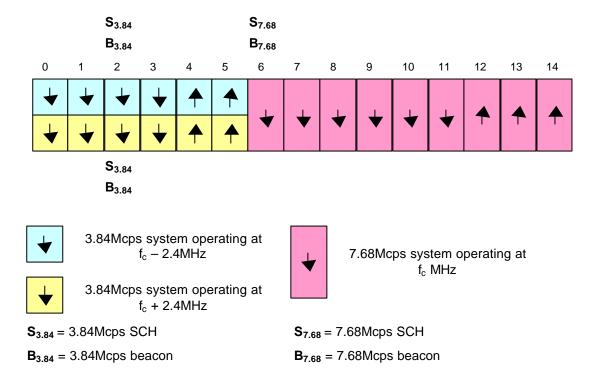

## 6.5.4 Servicing of 3.84Mcps TDD UEs under higher chip rate UTRAN

Both 3.84Mcps TDD UEs and higher chip rate UEs can be serviced by a higher chip rate UTRAN when the higher chip rate UTRAN is dual mode. An example timeslot arrangement for dual mode higher chip rate UTRAN is given in Figure 12. In this arrangement, two separate chip rates can be accommodated in the same frame; the two chip rates may operate independently of one another. Each chip rate carries its own SCH and beacon function. 3.84Mcps TDD UEs will camp on the cell according to the 3.84Mcps TDD SCH and beacon. Higher chip rate UEs will camp on to the cell according to the higher chip rate TDD SCH and beacon. Dual mode UEs may be "handed over" between the timeslots within the frame. Additional higher layer modifications would be needed to support this configuration.

Figure 12 – frame structure allowing 3.84Mcps TDD and higher chip rate UEs to be serviced by a dual mode higher chip rate UTRAN

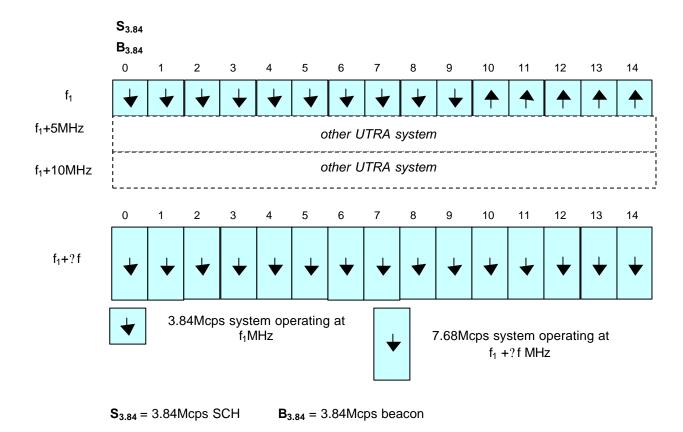

## 6.5.4 Operation of higher chip rate as an auxiliary downlink

Both 3.84Mcps TDD UEs and higher chip rate TDD UEs may be serviced when the higher chip rate TDD is used as an auxiliary downlink carrier. This operation is shown in Figure 13. 3.84Mcps TDD UEs are serviced by the 3.84Mcps carrier. Higher chip rate UEs can be serviced by the 3.84Mcps carrier (e.g. for uplink) and by the 7.68Mcps carrier (e.g. for downlink). The higher chip rate UE operates in a half-duplex mode.

Figure 13 - Example operation of higher chip rate TDD as an auxiliary downlink

## 6.6 Impact on other working groups

[Editor's note: Impact on RAN2, RAN3 and RAN4. Impacts may include signalling, RLC parameters, tests, channel models etc.]

## 6.7 Impact on Specifications

[Editor's note: discusses feasibility of incorporating higher chip rate UTRA TDD in 3GPP specifications at a technical level].

## 6.8 Signalling Impact

[Editor's note: discusses signalling required to support higher chip rate UTRA TDD].

## 6.9 Antenna Systems

[Editor's note: discussion of feasibility of transmit diversity schemes and "multiple input multiple output" (MIMO) systems].

## 6.10 Higher chip rates than 7.68Mcps

$[Editor's\ note: discussion\ of\ feasibility\ of\ chip\ rates\ higher\ than\ 7.68Mcps\ based\ on\ the\ studied\ reference\ 7.68Mcps\ system].$

## 7 Recommendations and Conclusions

[Editor's note: Conclusions on the feasibility and potential benefits of introducing higher chip rate UTRA TDD in UTRAN and, if appropriate, a recommendation to RAN Plenary on a potential work item time-frame and work plan].

## Annex A (normative): Link Level Simulation Assumptions

### A.1 Description of Bearer Services

Both circuit-switched speech/data and HSDPA-like packet-switched bearer services shall be evaluated.

### A.1.1 Release 99/4 Type

### A.1.1.1 Speech, 12.2 kbps

The normative reference measurement channels of 25.102 [8] annex A2.2 (DL) and 25.105 [9] annex A2.1 (UL) shall be used for simulation purposes. The spreading factors for both uplink and downlink are double those used for the 3.84Mcps system. Note that burst type 1 is used for both link directions for this service.

#### A.1.1.2 Circuit Switched Data, 384 kbps

The normative reference measurement channels of 25.102 [8] annex A2.5 (DL) and 25.105 [9] annex A2.4 (UL) shall be used for simulation purposes. The spreading factors for both uplink and downlink are double those used for the 3.84Mcps system. Note that burst type 2 is used for both link directions for this service.

## A.1.2 Release 5 Type (HSDPA)

A set of fixed-rate reference channels are simulated for HSDPA. These results are generated in order to enable mapping of a short-term channel quality metric to a probability of HS-DSCH transport block failure within a dynamic system-level simulation.

Interpolation between these fixed-rate reference channels is used to infer the performances of other transport block sizes and resource allocations within the dynamic system model.

The six fixed-rate reference channels of Table A.1 are defined for HSDPA simulation.

The physical resource allocation is the same for all of the six channels and is equal to 8 timeslots per 10ms TTI, each containing 4 codes at SF 32.

The redundancy and constellation version,  $X_{rv} = \{0,0,0,0\}$  is used for all reference channels.

Table A.1 – Fixed-Rate Reference Channels for HSDPA Link Simulation

| Fixed<br>Reference<br>Channel ID | Modulation<br>Type | Burst<br>Type | Available bits across<br>allocated physical<br>channels | Transport<br>Block Size | Approximate Code<br>Rate |

|----------------------------------|--------------------|---------------|---------------------------------------------------------|-------------------------|--------------------------|

| 1                                | QPSK               | 2             | 8832                                                    | 2912 bits               | 1/3                      |

| 2                                | QPSK               | 2             | 8832                                                    | 4384 bits               | 1/2                      |

| 3                                | QPSK               | 2             | 8832                                                    | 6592 bits               | 3/4                      |

| 4                                | 16 QAM             | 2             | 17664                                                   | 5856 bits               | 1/3                      |

| 5 | 16 QAM | 2 | 17664 | 8800 bits  | 1/2 |

|---|--------|---|-------|------------|-----|

| 6 | 16 QAM | 2 | 17664 | 13184 bits | 3/4 |

## A.2 Applicable Propagation Channels

Results shall be obtained in the following propagation channel types for all bearer services:-

- ?? AWGN

- ?? ITU Indoor to Outdoor Pedestrian A, 3kmph

- ?? ITU Indoor to Outdoor Pedestrian B, 3kmph

- ?? ITU Vehicular A, 30kmph

- ?? ITU Vehicular A, 120kmph

[Editor's note: The applicability of ITU Vehicular B to CS services is FFS]

## A.3 Deployment Specifics

The following deployment-specific parameters are assumed (Table A.2):-

Table A.2 – Deployment Specific Parameters for Link Simulation

| Parameter                      | Value           | Comments                                                                                                                                   |

|--------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Carrier Frequency              | 2000 MHz        |                                                                                                                                            |

| Chip Rate                      | 7.68 Mcps       |                                                                                                                                            |

| Tx Antenna Diversity at Node-B | OFF             |                                                                                                                                            |

| Tx Antenna Diversity at UE     | OFF             |                                                                                                                                            |

| Rx Antenna Diversity at Node-B | ON              | 2 antennas                                                                                                                                 |

| Rx Antenna Diversity at UE     | OFF             |                                                                                                                                            |

| Midamble Allocation Scheme, DL | Common Midamble |                                                                                                                                            |

| Midamble Allocation Scheme, UL | UE-specific     |                                                                                                                                            |

| Cell ID                        | 0               | Alternating scrambling code 0/1                                                                                                            |

| Kcell, burst type 1            | 8               |                                                                                                                                            |

| Kcell, burst type 2            | 8               | For the 7.68Mcps system burst type 2 uses a 512 chip midamble constructed using a 456-long base sequence.  Kcell = 4 and 8 are applicable. |

## A.4 Transmitter Assumptions

Transport channel processing for all bearer services shall comply with 25.222 [3].

The transmit filter shall consist only of an RRC filter with two-sided bandwidth 7.68MHz and roll-off factor? =0.22.

## A.5 Propagation Channel Simulation Assumptions

The channel is simulated at 2 times oversampling with respect to the chip rate.

Channel tap delay positions are quantised to the nearest integer ½ chip position.

A randomly selected delay of 0 or 1 "½ -chips" (both being equi-probable) shall be added to the entire channel impulse response in order to include the effects of sub-chip receiver timing offset.

Doppler shall conform to Jakes spectrum.

## A.6 Assumptions on Interference

#### A.6.1 Intra-cell

#### A.6.1.1 Downlink

It is assumed for circuit switched services that a total of 16 codes at SF 32 are transmitted each DL timeslot from the Node-B. This number comprises all codes allocated to the user of interest and all intra-cell interferers. This is in line with the highest interference level test scenarios of 25.102 [8] for demodulation of DCH for the equivalent 3.84Mcps system.

For HSDPA services, a higher code space loading is assumed with 24 codes at SF32 being transmitted from the Node-B.

The mean power of all transmitted SF32 codes is assumed to be the same. This leads to the following (Table A.3):-

Number of SF32 DPCH or Simulated Number of  $DPCH_0 \_E_c$  $DPCH_0 \_E_c$ **HS-PDSCH Interfering Bearer Codes Occupied** by Bearer per Codes at SF32  $E_c$ **Timeslot** per Timeslot 2 14 -12.04 dB -12.04 dB 12.2 kbps Speech -0.58 dB 384 kbps Data 8 -12.04 dB -12.04 dB -3.01 dB 8 -13.8 dB **HSDPA** 20 -13.8 dB -0.79 dB 4 Reference Channels

Table A.3 – Interference Characteristics for Downlink Simulation

#### A.6.1.2 Uplink

The following scenarios (Table A.4) are considered for the uplink simulations. As for the downlink these are in line with the highest interference level test scenarios of 25.105 [9] for demodulation of DCH for the equivalent 3.84Mcps system. One half of the code space is occupied in total, comprising the user of interest and all intra-cell interferers.

Table A.4 - Interference Characteristics for Uplink Simulation

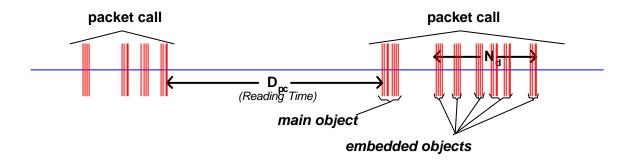

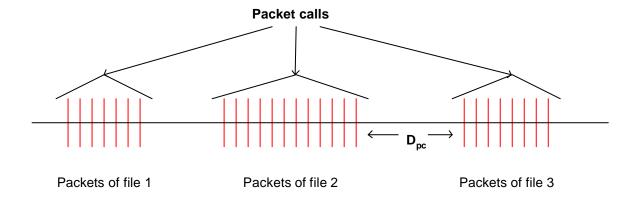

| Bearer           | Resource<br>Occupied by<br>Bearer | Number and SF<br>of Interfering<br>Codes per Slot | $\mathbf{DPCH} \; \frac{E_c}{I_{or}}$ | $\frac{DPCH_{0} - E_{c}}{I_{or}}$ | $\frac{? DPCH_{0} - E_{c}}{I_{or}}$ |