### TSGR1#7bis(99)f04

TSG RAN WG1#7bis Kyongju, Korea October 3 – 4, 1999

Agenda Item: 4.2 AH14

**Source:** Golden Bridge Technology

Title: Proposed text changes to 25.211 (CPCH sections)

**Document for:** Discussion and Approval

Section 5.2.2.2.2

### CPCH access preamble part

Similar to 5.2.2.1.2 5.2.2.1.2 (RACH preamble part). The RACH preamble signature sequences eould shall be used. The number of sequences used could be less than the ones used in the RACH preamble. The scrambling code could either be chosen to be a different code segment of the Gold code used to form the scrambling code of the RACH preambles (see-[4] [4] for more details) or could be the same scrambling code in case the signature set is shared.

Section 5.2.2.2.3

# CPCH collision detection preamble part

Similar to <u>5.2.2.1.2</u> (RACH preamble part). The RACH preamble signature sequences are used. The scrambling code is chosen to be a different code segment of the Gold code used to form the scrambling code for the RACH and CPCH preambles (see [41] [4] for more details).

Section 5.2.2.2.4

#### CPCH power control preamble part

The power control preamble segment is aA [10] ms DPCCH Power Control Preamble (PC-P). The following Table xxx is identical to Rows 2 or 4 or 5 of Table 2 Table 2 in 5.2.1 5.2.1 and is the recommended DPCCH fields which only includes Pilot, FBI and TPC bits. Power Control Preamble length is ffs.

Table xxx: DPCCH fields for CPCH power control preamble segment

| Channel Bit Rate (kbps) | Channel<br>Symbol<br>Rate<br>(ksps) | SF         | Bits/<br>Frame | Bits/<br>Slot | N_pilot  | N <sub>TPC</sub> | N <sub>TFCI</sub> | N <sub>FBI</sub> |

|-------------------------|-------------------------------------|------------|----------------|---------------|----------|------------------|-------------------|------------------|

| <u>15</u>               | <u>15</u>                           | <u>256</u> | <u>150</u>     | <u>10</u>     | <u>8</u> | 2                | <u>0</u>          | <u>0</u>         |

| <u>15</u>               | <u>15</u>                           | <u>256</u> | <u>150</u>     | <u>10</u>     | <u>7</u> | 2                | <u>0</u>          | 1                |

| <u>15</u>               | <u>15</u>                           | <u>256</u> | <u>150</u>     | <u>10</u>     | <u>6</u> | 2                | <u>0</u>          | 2                |

Section 5.2.2.2.5

## CPCH message part

Figure 1 in-5.2.1 5.2.1 shows the structure of the CPCH message part. Each message consists of up to N\_Max\_frames 10 ms frames. N\_Max\_frames is a MAC layer parameter. Each 10 ms frame is split into 15 slots, each of length  $T_{\text{slot}} = 2560$  chips. Each slot consists of two parts, a data part that carries Layer 2 information and a control part that carries Layer 1 control information. The data and control parts are transmitted in parallel.

The data part consists of  $10*2^k$  bits, where k = 0.1.2, 3, 4, 5, 6, corresponding to spreading factors of 256.128.64, 32, 16, 8, 4 respectively. Note that various rates might be mapped to different signature sequences.

.The spreading factor for the <u>UL-DPCCH</u> (message control part ) will be <u>256. <del>256. The SF for the DL-DPCCH (message control part) shall be 512. The following Table xxx shows the DL-DPCCH fields (message control part) which is identical to the first two rows of Table 10 in section <u>5.3.2. The entries in Table 1 Table 1 corresponding to spreading factors of <u>256.64</u> and below and <u>Table 2 Table 1 [both in section <u>5.2.15.2.1]</u> apply to the DPDCH and <u>UL-DPCCH fields respectively for the CPCH message part.</u></u></del></u></u>

#### Table xxx: DPDCH and DPCCH fields

| Channel Bit Rate (kbps) | Channel Symbol Rate | <u>SF</u>  | Bits/Frame   |              |            |           | Bits/Slot          |                    | DPCCH Bits/Slot  |                  |                    |

|-------------------------|---------------------|------------|--------------|--------------|------------|-----------|--------------------|--------------------|------------------|------------------|--------------------|

|                         | (ksps)              |            | <u>DPDCH</u> | <u>DPCCH</u> | <u>TOT</u> |           | N <sub>Data1</sub> | N <sub>Data2</sub> | N <sub>TFC</sub> | N <sub>TPC</sub> | N <sub>Pilot</sub> |

| <u>15</u>               | <u>7.5</u>          | <u>512</u> | <u>60</u>    | <u>90</u>    | <u>150</u> | <u>10</u> | <u>2</u>           | 2                  | 0                | <u>2</u>         | <u>4</u>           |

| <u>15</u>               | <u>7.5</u>          | <u>512</u> | <u>30</u>    | <u>120</u>   | <u>150</u> | <u>10</u> | <u>0</u>           | 2                  | <u>2</u>         | <u>2</u>         | <u>4</u>           |

#### Section 7.4

# PCPCH/AICH timing relation

Transmission of random access bursts on the PCPCH is aligned with access slot times. The timing of the access slots is derived from the received Primary CCPCH timing The transmit timing of access slot n starts  $n\times20/15$  ms after the frame boundary of the received Primary CCPCH, where n=0,1,...,14. In addition, transmission of access preambles in PCPCH is limited to the allocated access slot subchannel group which

is assigned by RNC to each CPCH set. Twelve access slot subchannels are defined and PCPCH may be allocated all subchannel slots or any subset of the twelve subchannel slots. The access slot subchannel identification is identical to that for the RACH and is described in Table 6 of section 6.1 of TS25.214

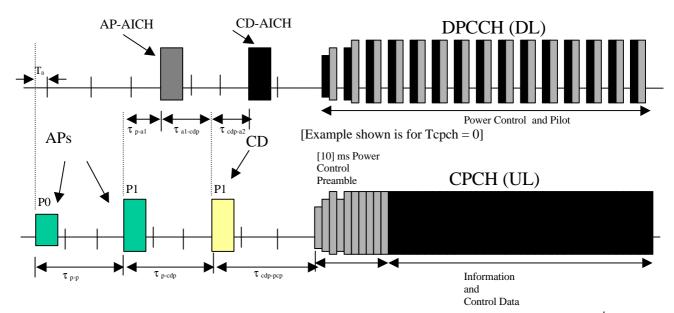

Everything in the previous section [PRACH/AICH] applies to this section as well. The timing relationship between preambles, AICH, and the message is the same as PRACH/AICH. Note that the collision resolution preambles follow the access preambles in PCPCH/AICH. However, the timing relationships between CD-Preamble and CD-AICH is identical to RACH Preamble and AICH. The timing relationship between CD-AICH and the Power Control Preamble in CPCH is identical to AICH to message in RACH. However, the set of values for T<sub>epch</sub> is TBD. As an example, T<sub>epch</sub>-timing parameter is identical to the PRACH/AICH transmission timing parameter. Wwhen T<sub>epch</sub> is set to zero or one or

Note that a1 corresponds to AP-AICH and a2 corresponds to CD-AICH.

$\tau_{p-p} = \frac{\text{Time between Access Preamble (AP) to the next AP.}_{\text{-}}$  is either 3 or 4 access slots, depending on  $T_{\text{epeh.}}$   $\tau_{\text{next slor}} = \text{Time to next available access slot, between Access Preambles.}$

Minimum time = 3.75ms + 1.25ms X Tcpch

Maximum time = 1.25msec X 12 = 15 msec

Actual time is time to next slot (which meets minimum time criterion) in allocated access slot subchannel group.

$\tau_{p-al}$  = Time between Access Preamble and AP-AICH has two alternative values: 7680 chips or 12800 chips, depending on  $T_{cpch}$

$\tau_{\text{al-cdp}}$  = Time between receipt of AP-AICH and transmission of the CD Preamble has one value: 7680 chips.

$\tau_{p\text{-}cdp} = \text{Time}$  between the last AP and CD Preamble. is either 3 or 4 access slots, depending on  $T_{cpch}$

$\tau_{cdp\text{-}a2}$  = Time between the CD Preamble and the CD-AICH has two alternative values: 7680 chips or 12800 chips, depending on  $T_{cpch}$

$\tau_{cdp\text{-pcp}}$ = Time between CD Preamble and the start of the Power Control Preamble is either 3 or 4 access slots, depending on  $T_{cpch}$ .

Figure 1 shows the timing of the CPCH uplink transmission with the associated DPCCH control channel in the downlink.

<u>Figure 26 illustrates the PCPCH/AICH timing relationship when T<sub>cpch</sub> is set to 0 and all access slot subchannels are available for PCPCH.</u>

Figure- $\underline{26}$   $\underline{26}$ : Timing of PCPCH and AICH transmission as seen by the UE, with  $T_{cpch}$ = 0.